13-73-10/55

# HITACHI ANALOG COMPUTER 505 OPERATION MANUAL

@Hitachi, Ltd.

M 9-96

# HITACHI ANALOG COMPUTER 505 CONTENTS

| SECTION I - INTRODUCTION                   | 4               |

|--------------------------------------------|-----------------|

| SECTION II - THE HITACHI 505 COMPUTER      | 4               |

| 1. GENERAL DESCRIPTION OF HITACHI 505 .    | 4               |

| 2. OPERATING CONSIDERATIONS                | 8               |

| a. Preliminary Operating Considerati       | ons 8           |

| b. Pre-Patch Panel Insertion and Rem       | oval 12         |

| c. Amplifier Balance                       |                 |

| d. Changing Computational Components       | 15              |

| 3. MONITORING AND CONTROL                  | 21              |

| a. Output Selector SL-251                  | 21              |

| b. Overload Indicator OL-251               | 24              |

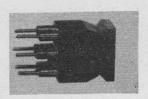

| c. Digital Voltmeter DV-251                | 24              |

| d. Multi-Range Voltmeter (in the Con       | ntrol Panel) 26 |

| e. Reference Potentiometer (in the (Panel) | Control 27      |

| f. Mode Control (in the Control Pan        | el) 27          |

| g. Trunks                                  | 31              |

| h. Slave Switches (in the Control P        | anel) 32        |

| i. Readout Devices                         | 34              |

| j. Function Switches                       | 34              |

| k. Power Switches (in the Control F        | Panel) 35       |

| 4. POTENTIOMETERS                          | 35              |

| 5. OPERATIONAL AMPLIFIER                   |                 |

| a. General Considerations                  |                 |

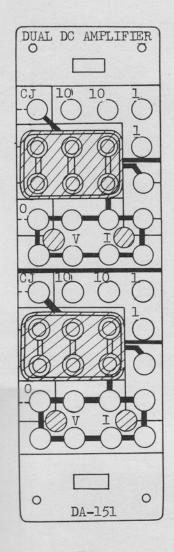

| b. 505 Operational Amplifier DA-15         | 1 47            |

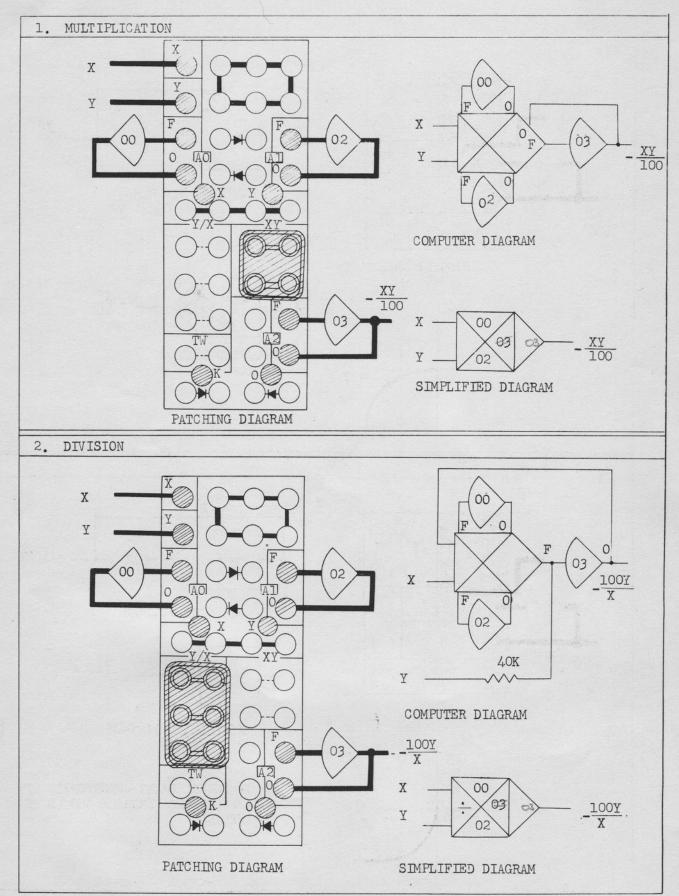

|     | 6.    | QUA  | RTER-SQUARE MULTIPLIER EM-151                             | 56  |

|-----|-------|------|-----------------------------------------------------------|-----|

|     |       | a.   | Multiplication                                            | 58  |

|     |       | b.   | Division                                                  | 62  |

|     | 7.    | FUN  | CTION GENERATORS                                          | 64  |

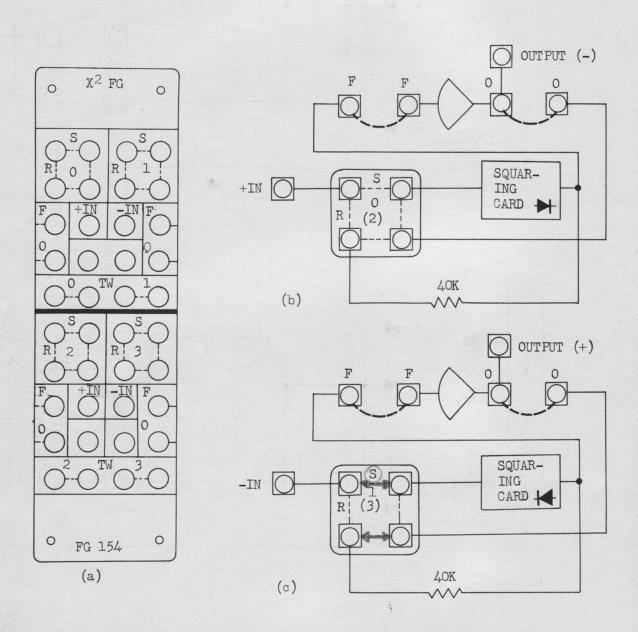

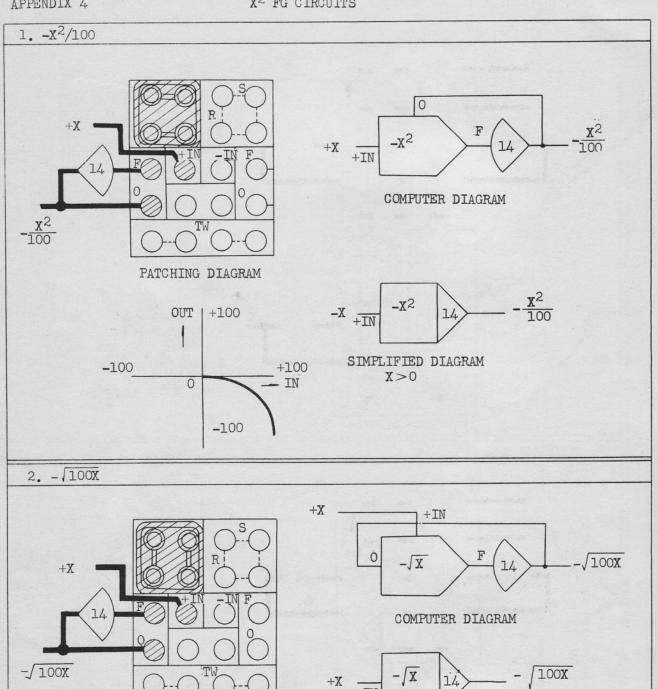

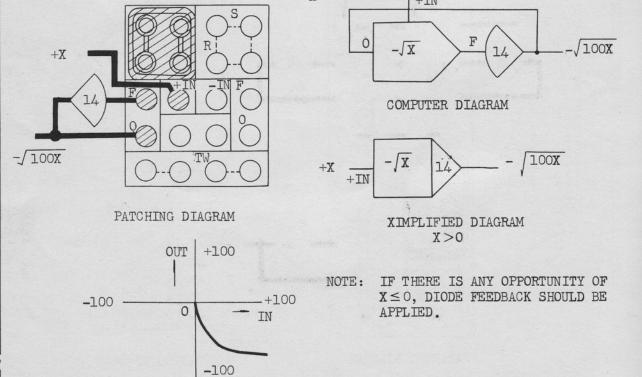

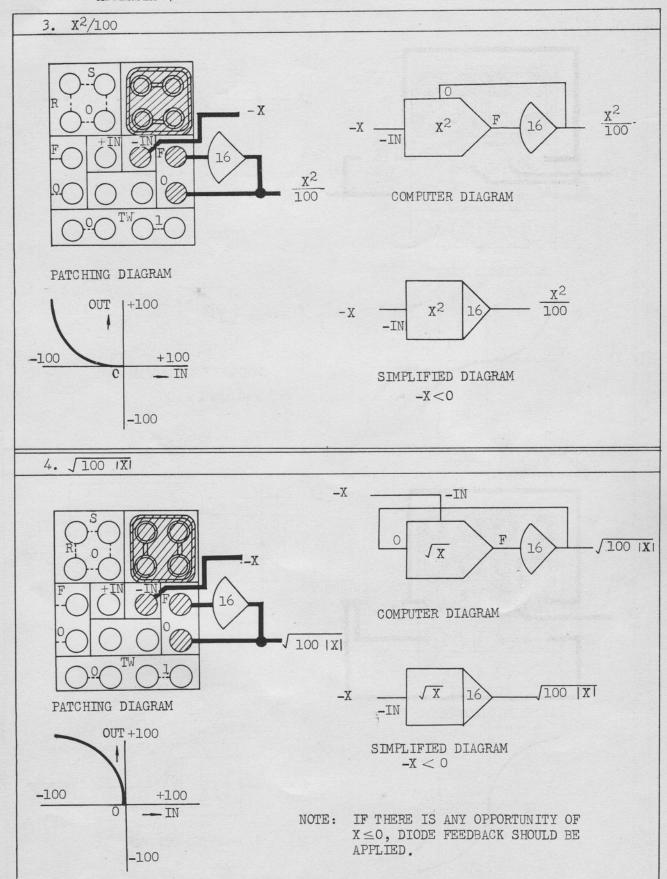

|     |       | a.   | X <sup>2</sup> Fixed Function Generator FG-154A           | 64  |

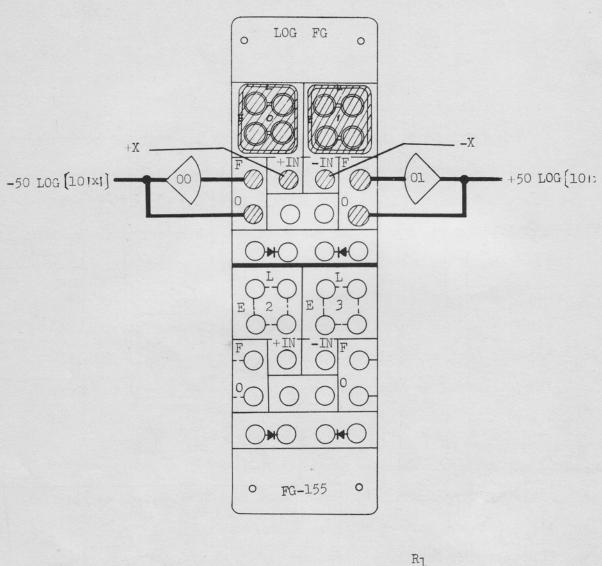

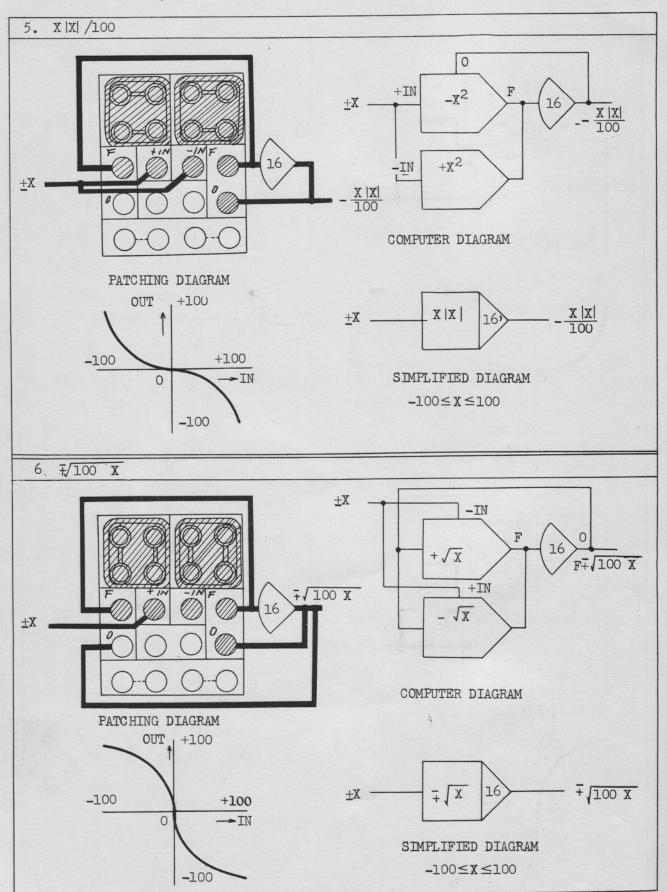

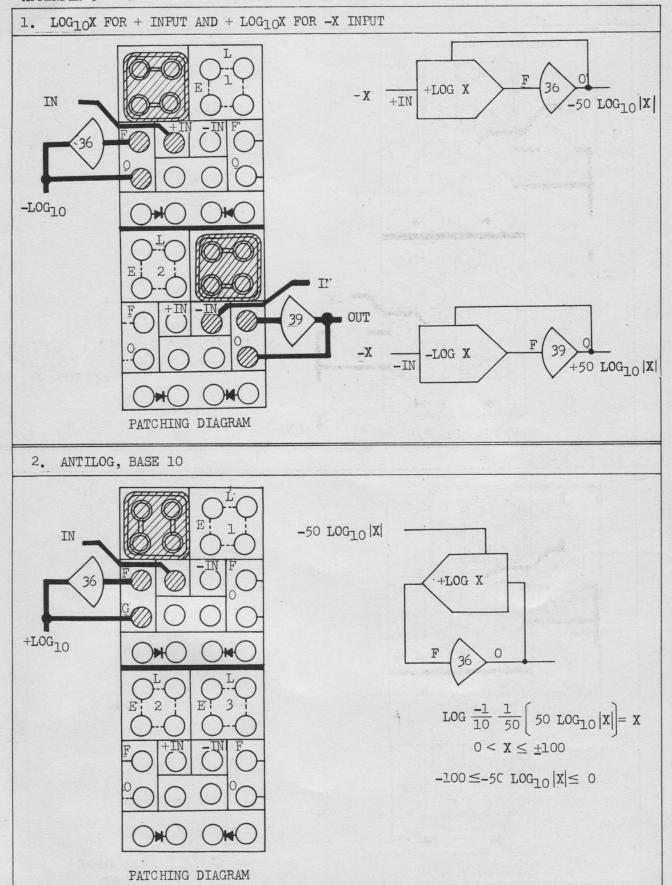

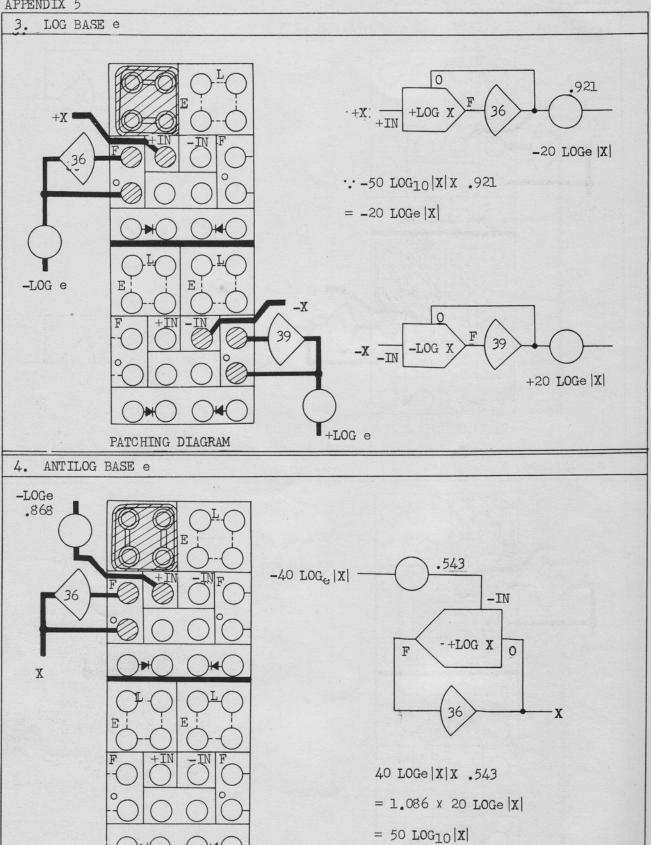

|     |       | b.   | Log X Fixed Function Generator FG-155A                    | 67  |

|     |       | c.   | Trigonometric Fixed Function Generator FG-153A            | 67  |

|     |       | d.   | Variable Function Generator FG-151                        | 67  |

|     |       | e.   | Variable Function Generator FG-152                        | 79  |

|     |       | f.   | Variable Function Generator FG-157                        | 81  |

|     | 8.    | CON  | MPARATORS CP-151, CP-152                                  | 85  |

|     | 9.    | FRE  | CE DIODES FD-151                                          | 89  |

|     | 10.   | TR   | ANSFER DELAY ELEMENT TD-151                               | 89  |

|     | 11.   | AU.  | FOMATIC OPERATOR AO-151                                   | 94  |

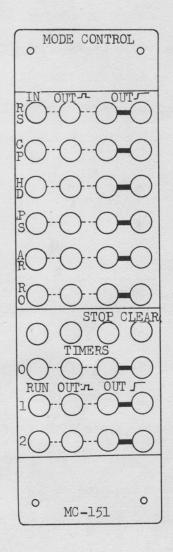

|     | 12.   | MO   | DE CONTROL PANEL MC-151                                   | 94  |

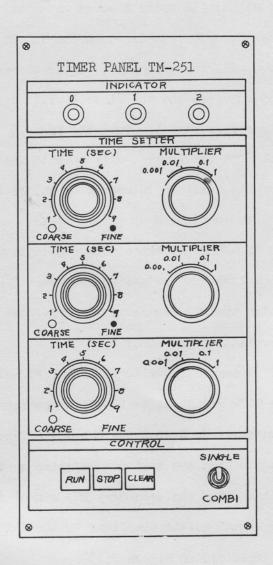

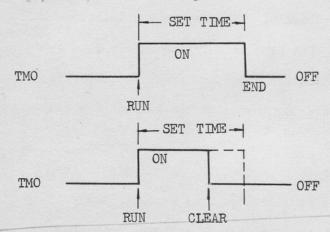

|     | 13.   | TI   | MERS                                                      | 98  |

|     | 14.   | RE   | PETITIVE OPERATION                                        | 102 |

| SE  | CTIO  | 1 II | I - MAINTENANCE SEPARATED                                 |     |

| n H | TTACE | A IF | NALOG COMPUTER PROGRAM MANUAL" will explain the programmi | ing |

| te  | chni  | que  | for HITACHI 505 Computer.                                 |     |

| Th  | ne Ma | nual | is common in programming for all kinds of HITACHI Analog  | g   |

| Co  | mput  | er.  |                                                           |     |

#### ILLUSTRATIONS

| Figure<br>Number | Title                                                                 |

|------------------|-----------------------------------------------------------------------|

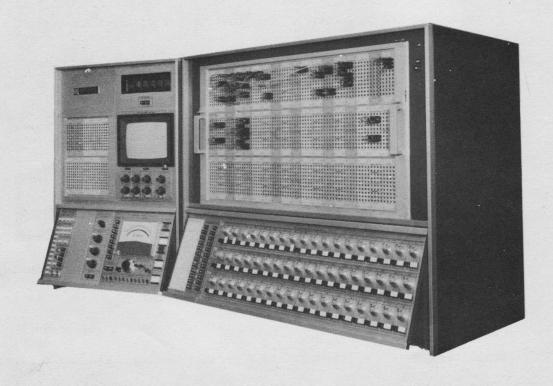

| 2.1-1            | Typical 505, Front View                                               |

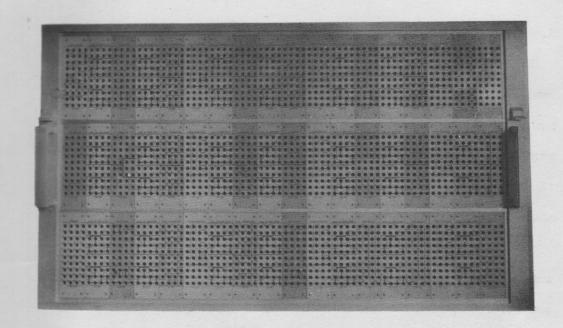

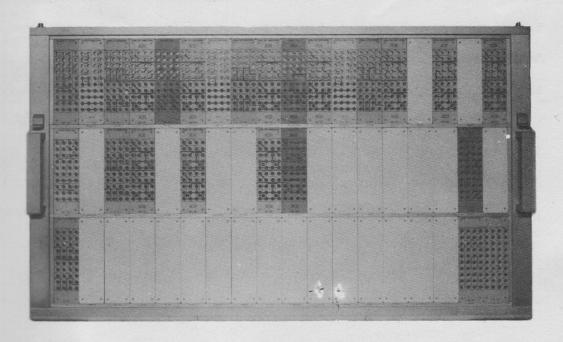

| 2.1-2            | Pre-Patch Panel, Modular Layout                                       |

| 2.2-1            | Amplifier with Six-Connector Bottle-Plug Providing Feedback           |

| 2.2-2            | DVM Front View                                                        |

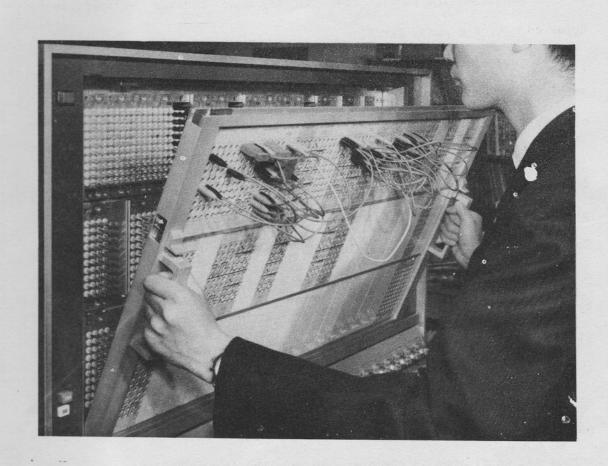

| 2.2-3            | Pre-Patch Panel Insertion                                             |

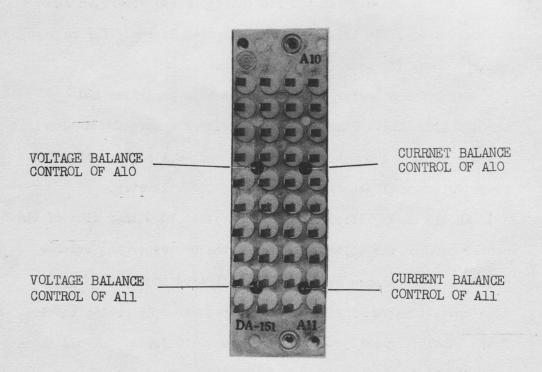

| 2.2-4            | Amplifier Balance Control Location                                    |

| 2.2-5            | Computer Component Module Assignment Areas                            |

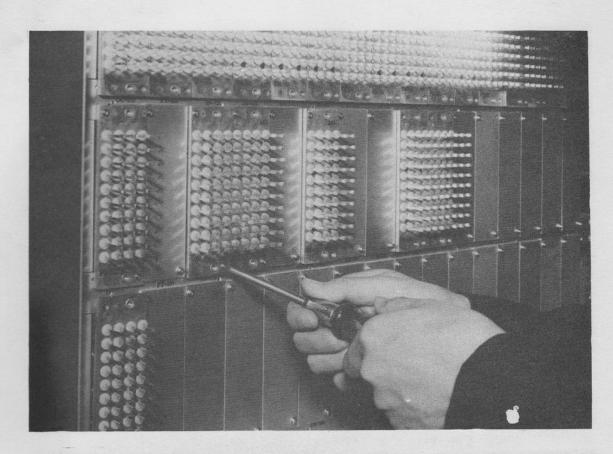

| 2.2-6            | Removal of Computing Module                                           |

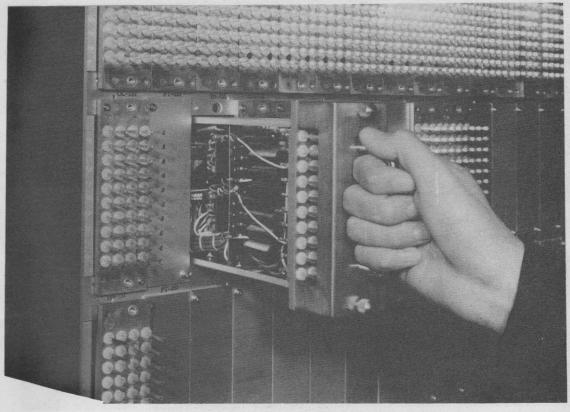

| 2.2-7            | Patching Block Replacement                                            |

| 2.3-1            | HITACHI 505 Control Area                                              |

| 2.3-2            | Readout Panel OC-151 Patching Block and DVM/VM to SEL Patching        |

| 2.3-3            | Simplified Schematic of Reference Potentiometer                       |

| 2.3-4            | Connecting Area, Rear the Computing Console                           |

| 2.4-1            | Potentiometer Patching Unit PT-151 and Potentiometer Panel PT-251     |

| 2.4-2            | Potentiometer Schematic Showing ein = 100 volts                       |

| 2.4-3            | Potentiometer Loading                                                 |

| 2.4-4            | 505 Potentiometer Circuits, Simplified Schematic                      |

| 2.4-5            | Potentiometer Schematic and Computer Diagram Symbols                  |

| 2.5-1            | Operational Amplifier, Simplified Block Diagram                       |

| 2.5-2            | Operational Amplifier, Simplified Schematic and Patching Block Layout |

| 2.5-3            | Summer Amplifier Patching                                             |

| 2.5-4            | Integrator Patching and Simplified Block Diagram                      |

| 2.5-5  | Integrator Amplifier and Simplified Schematic                          |

|--------|------------------------------------------------------------------------|

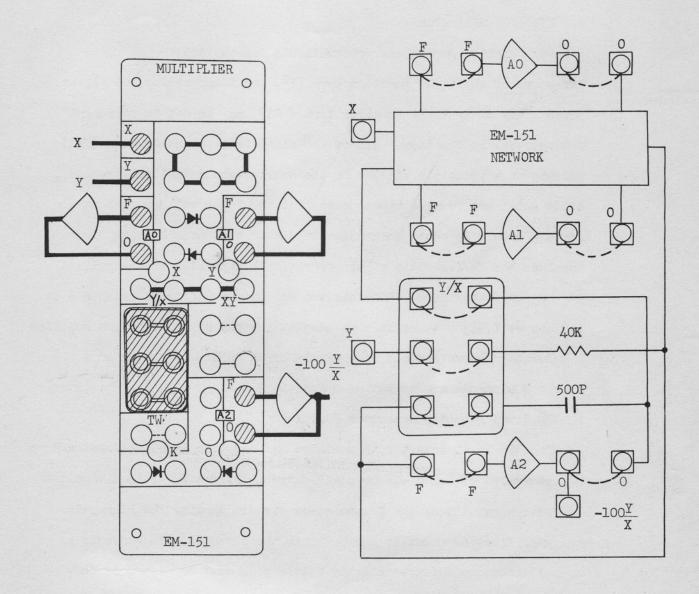

| 2.6-1  | Multiplier, Simplified Block Diagram                                   |

| 2.6-2  | Squaring Circuit, Simplified Schematic                                 |

| 2.6-3  | Multiplier, Simplified Block Diagram and Patching Block Layout         |

| 2.6-4  | Multiplication Patching and Simplified Schematic                       |

| 2.6-5  | Division Patching and Simplified Schematic                             |

| 2.7-1  | X2 FG, Simplified Schematic Block Diagram                              |

| 2.7-2  | X2 FG, Patching and Simplified Schematic                               |

| 2.7-3  | Log X FG Patching and Simplified Schematic                             |

| 2.7-4  | Trigonometric FG, Simplified Schematic and Patching Block Layout       |

| 2.7-5  | sinX Patching and Simplified Schematic                                 |

| 2.7-6  | cosX Patching and Simplified Schematic                                 |

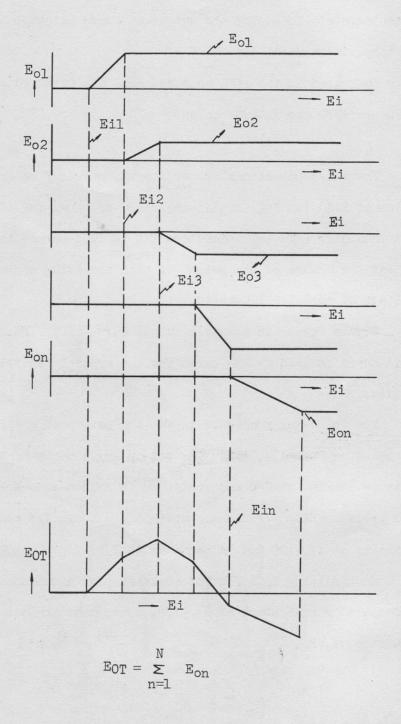

| 2.7-7  | Principle of VFG                                                       |

| 2.7-8  | VFG FG-151, Simplified Block Diagram and Patching Block Layout         |

| 2.7-9  | VFG FG-151, Separate VFG Patching                                      |

| 2.7-10 | VFG FG-151, Combined VFG Patching                                      |

| 2.7-11 | Location of VFG's and VFG setting                                      |

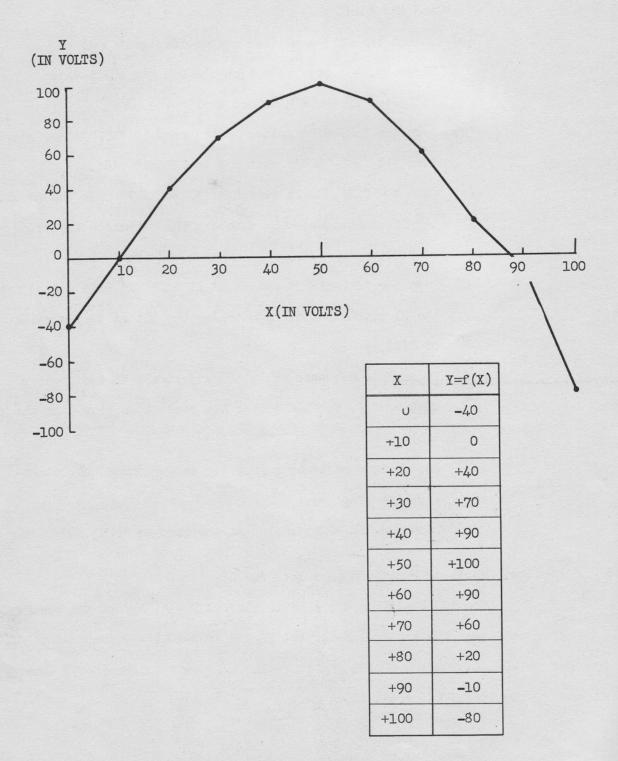

| 2.7-12 | Sample Output Curve                                                    |

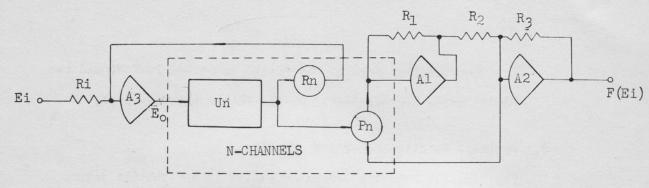

| 2.7-13 | Principle of VFG FG-157                                                |

| 2.7-14 | VFG FG-157, Simplified Block Diagram and Patching Block Layout         |

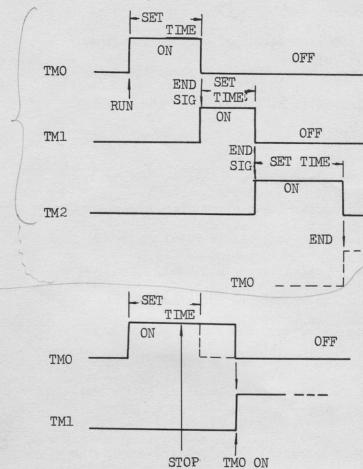

| 2.7-15 | Timer Operation                                                        |

| 2.8-1  | Comparator Simplified Schematic and Patching Block Layout              |

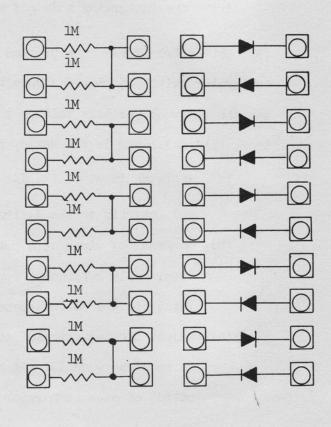

| 2.9-1  | Free Diodes Schematic and Patching Block Layout                        |

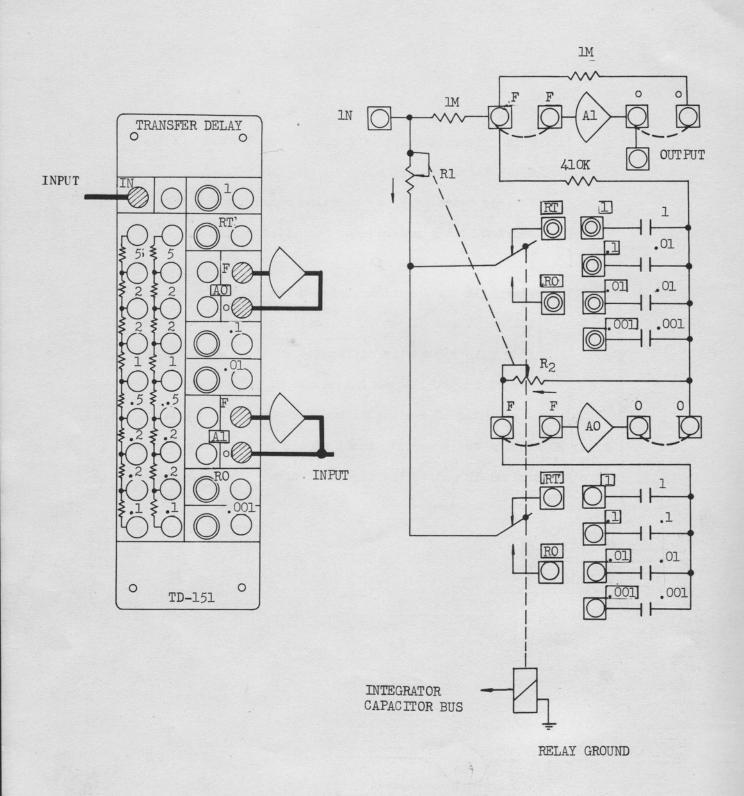

| 2.10-1 | Transfer Delay Element, Simplified Schematic and Patching Block Lavout |

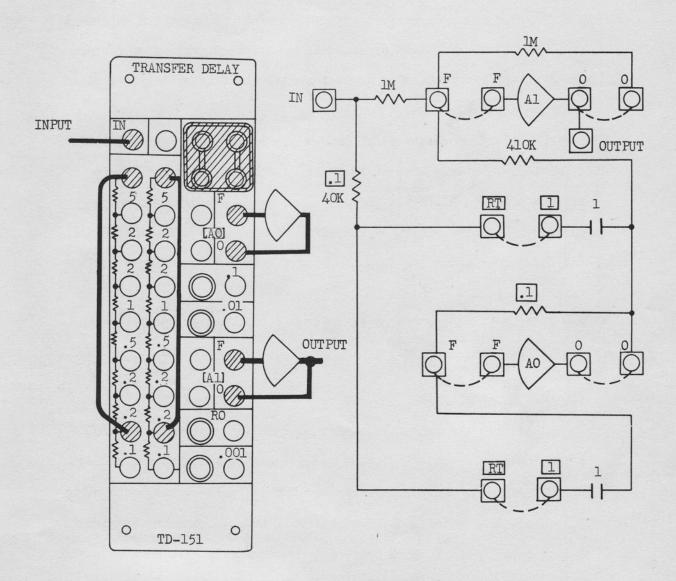

| 2.10-2 | Transfer Delay Element, Typical Patching and Simplified Schematic                     |

|--------|---------------------------------------------------------------------------------------|

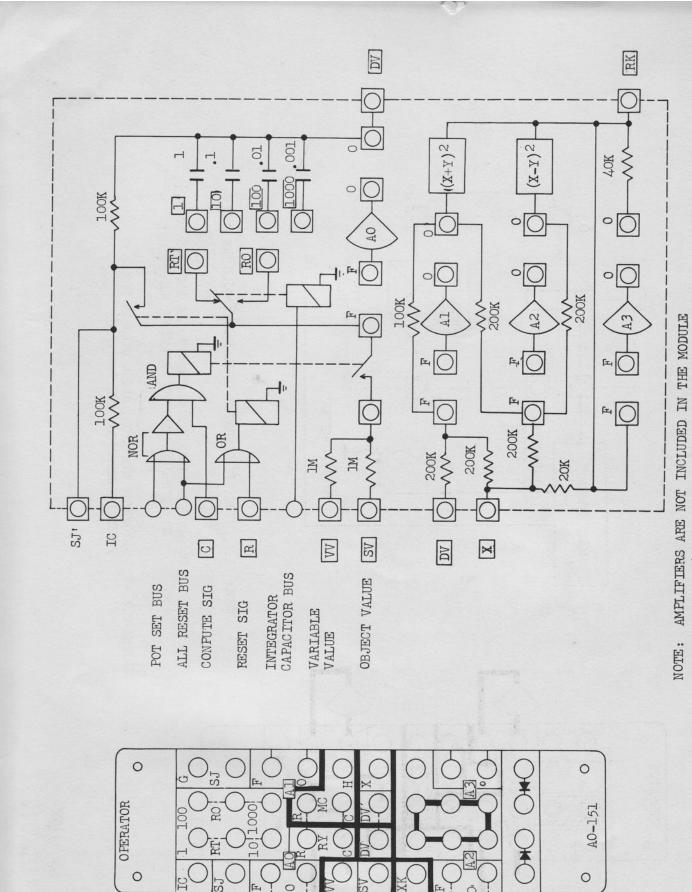

| 2.11-1 | Automatic Operator, Simplified Schematic and Patching Block Layout                    |

| 2.11-2 | Automatic Operator, Block Diagram for Typical<br>Connection and Patching Block Layout |

| 2.12-1 | Mode Control Panel Patching Block Layout                                              |

| 2.13-1 | Timer Panel, TM-251                                                                   |

| 2.13-2 | Timer Operation                                                                       |

#### SECTION I

#### INTRODUCTION

Many scientific problems studied today in various fields involve the solution of partial or ordinary differential equations. It is the exception, rather than the rule, that the problems admit exact analytic solutions. The modern analog computer, such as the Hitachi 505, provides a convenient method for obtaining numerical solutions to such problems as well as enabling the scientist to study the effect of changes in the physical system.

The method of problem solution in an analog computer is quite simple. The computer is used to "build" an electronic analogy which obeys the same set of differential equations as the physical problem to be studied. Once this model has been constructed, experiments may be performed on this model in lieu of experiments on the physical system. Investigations which might be difficult to carry out on the actual system become quite feasible with this technique. For example, a physician may wish to study the effect on blood pressure in a certain portion of the brain in the event that a patient loses an arm. It is unlikely that this experiment would be performed by any means other than simulation!

Variable corresponds to, or is analogous to, a computer voltage. As these voltages are readily available for measurement, instrumention is employed to measure the problem variables as in an actual system. Solutions may be continuously displayed on a readout oscilloscope, permanently plotted on a strip chart or x-y plotter, or numerically

evaluated by means of a voltmeter or digital voltmeter.

The detailed steps necessary for problem solution will be discussed in detail in a later section. Briefly, one must first construct a mathematical model for the system to be studied. Often such a model is not available. In this case, there are analog computer techniques available for generating a model from deta taken from the physical system. The next step involves the construction of a computer "block diagram" (an array of summing amps, integrators, etc.) which obeys the same differential equations as the system model. This diagram is then used to connect computing elements utilizing the patchboard. Since the patchboard may be removed from the computer and another patchboard inserted, it is not necessary to use computer time othersthan for actual computation.

The problem is now ready for computer solution. After mounting the proper patchboard, the potentiometers ("Pots") are set to correspond to the physical problem constants. The computer solution is now obtained by pressing the "COMPUTE" button. Problem variables may then be observed and recorded as desired. Additional runs may be made with different physical constants, problem variables, initial conditions, etc.

This manual describes the computer operation and programming in detail. It should be emphasised that a knowledge of electrical engineering is not necessary to success fully operate an analog computer. The block diagram approach used in this manual is common in many fields. The manual describes the general computer operating controls first.

This is followed by a module by module description of each "black box",

patchboard connections. Basic programming is explained in the program manual at an introductory level. The detailed example given in this section may be used as a model for the user's particular problem set up in the manual, titled "Applications", explains the special features of the Hitachi 505 for more advanced techniques. It includes function generation, transfer function simulation, and partial differential equation solution. Helpful suggestions for the use of the automatic operation unit in optimization problems and the Timer and Logic Operations board in iterative methods is also included.

#### SECTION II

## THE HITACHI 505 COMPUTER

# 1. GENERAL DESCRIPTION OF HITACHI 505

The Hitachi 505 is a medium size desk-top general purpose analog computer having a wide variety of applications. This computer may be installed in any office or laboratory without special considerations as to power or temperature control. The power consumption is quite low, easily handled by normal office wiring. Since this computer supplies its own internal operating environment by means of an oven, it does not depend on an accurate external temperature control. The heat delivered to the room by the unit itself is about the same as that delivered by a medium size laboratory oscilloscope.

The Hitachi 505 is modular in concept with solid state components used throughout\*. The modular arrangement of the computer permits special machine configurations depending on the user's requirements. The component arrangement allows simplified wiring. Color coding of the modules aids in rapid identification of elements and simplifies wiring checks.

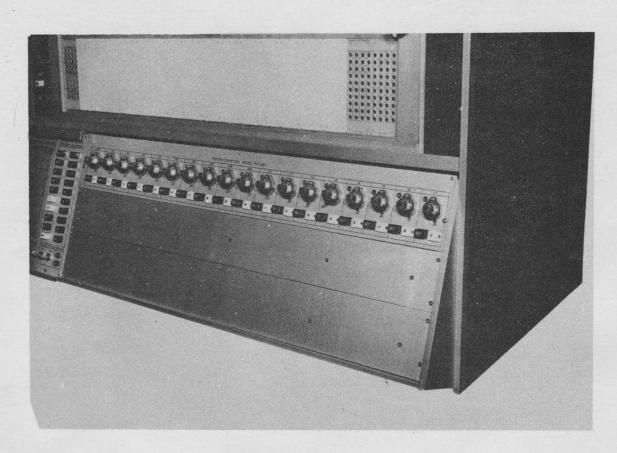

The computer is housed in two cabinets, the computer main frame and the control console. These units may be easily separated for transportation. The main computer console contains the patchboard with the associated computing components mounted in an oven directly behind the patchboard. Beneath the patch panel is a panel containing the amplifier overload indicators, the readout addressing system, and the coefficient potentiometers with their associated indicator lamps,

<sup>\*</sup> With the exception of the oscilloscope tube and a high voltage rectifier in it.

addressing buttons, and label plates. A control located immediately to the left of the patchboard operates the motor drive for removing or replacing the patchboard. The lower panel of the main computing console is tilted toward the operator for ease of operation.

The power supply for the computing elements is located in the bottom rear of the cabinet. It is easily removed for service or transportation.

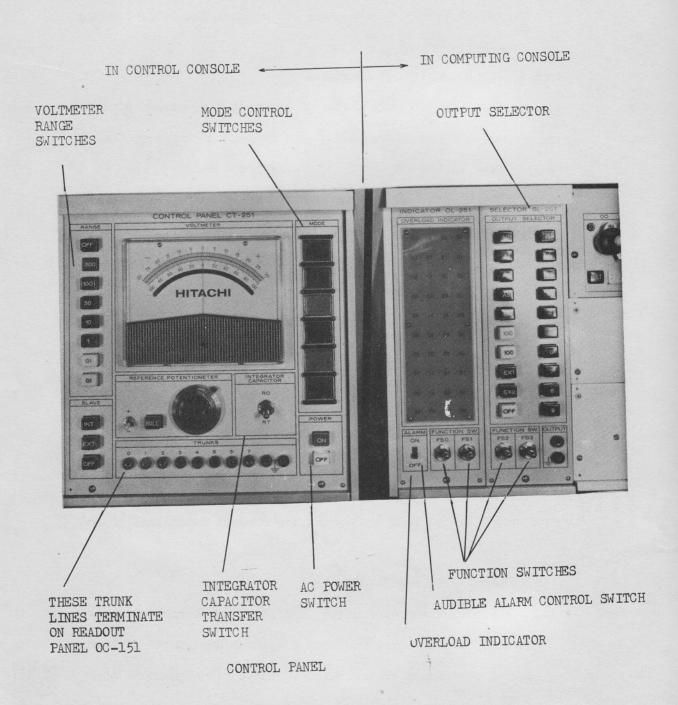

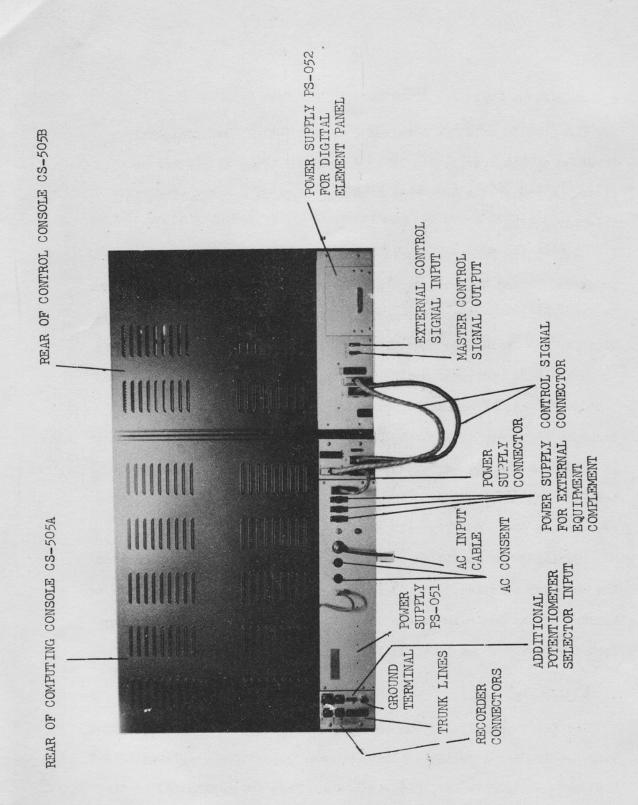

The control console contains the control panel, the oscilloscope, the iterative operation timer, the digital logic unit, and the digital voltmeter. The control panel, located in the lower right hand side of the control console, contains the manual mode control switches, a coltmeter, the reference potentiometer, and some external trunk terminals. Immediately above this unit is a three channel oscilloscope with electronically generated scales. The digital voltmeter mounted above this oscilloscope may be used for accurate potentiometer setting and solution readings. The iterative operation timer, which may be used for sequential mode control, is located in the lower left corner of the control console. The digital logic unit, mounted directly above the timer module, contains various types of patchable logic.

NOTES: 1. THE DISPOSITION CHANGED SLIGHTLY IN THE LATER PRODUCTS.

2. ONE MORE COMPUTING CONSOLE MAY BE ADDED TO THE RIGHT OF THE ABOVE COMPUTER.

FIGURE 2.1-1 TYPICAL 505, FRONT VIEW

FULLY EQUIPPED

HALF EQUIPPED

FIGURE 2.1-2 PRE-PATCH PANEL MODULAR LAYOUT

### 2. OPERATING CONSIDERATIONS

The Hitachi 505 (Figure 2.1-1) is shipped complete with all components in place except power supply and DVM. Each unit is completely calibrated and adjusted at the time of manufacture. After performing the simple installation and check procedure outlined in the maintenance manual, and connecting the unit to a suitable power source, the computer is ready for operation.

The current limiting circuits protect the reference supplies and all active operational elements from damage due to shorting to ground, or to each other. Thus an errant patching connection (shorting the plus reference to ground for example) will not adversely effect the supplies (output current drops to zero) nor will the reference supply fuse blow. In addition, the surface of Pre-Patch Panel is covered with coloured plastic plates (except frame and handles) reducing shorting-out of hanging patch cords.

## a. Preliminary Operating Considerations

The following steps are recommended prior to operating the Hitachi 505 to prevent possible false trouble indications.

(1) Ascertain that each operational amplifier has a six connector bottle plug or a combination of bottle plugs equal to a six connector bottle plug, properly placed and seated as shown in Figure 2.2-1. This provides the amplifiers with feedback and prevent them from overloading during the problem solution.

(b) SIX-CONNECTOR BOTTLE-PLUG

(a)

FIGURE 2.2-1 AMPLIFIER WITH SIX CONNECTOR BOTTLE-PLUG PROVIDING FEEDBACK

DVM DV-25l ("RATIO-VOLT" SWITCH ADDED IN LATER MODEL)

DVM El 620

FIGURE 2.2- DVM FRONT VIEW

The procedure for inserting and removing the Pre-Patch Panel is described in Paragraph 2.b.

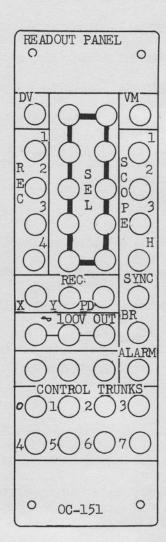

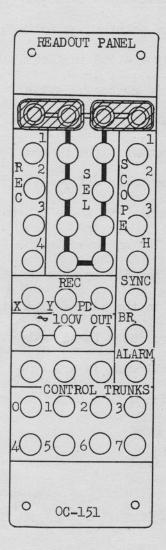

- (2) Patch the Digital Voltmeter (DVM) and multi-range voltmeter (VM) to the selector readout system. (See Figure 2.3-2 and Paragraph 2.c. of this section for a description of the selector system operation)

- (3) Apply power to the computer, then Pot Set mode will appear. Initially the overload lamps of the operational amplifiers will light; after a few seconds all of the lamps should extinguish.

- (4) Check the various supply voltages of the computer. All power supply outputs are connected to the voltmeter switch in front of the power supply through appropriate scaling resistors; the check may be accomplished simply and rapidly.

- (5) Check the plus and minus reference supplied for readout on the DVM by selecting 100 (red for plus) and 100 (blue for minus). See Paragraph 3.a.

- (6) Allow about thirty minutes warm-up time; this assures that the computing components, (including the DVM and oscilloscope) are up to normal operating temperature. Ground the DVM input termination (designated on the OC-151 READOUT PANEL), and confirm the reading is within 000.00 plus or minus one bit. Other adjustment for DVM will be necessary according to Model of DVM, for DV-251, the zero check is the only step necessary to assure the correct operation.

- (7) In the POT SET mode of the computer (POT SET button on the control panel, model CT-251 depressed), closed relay contacts provide a feedback circuit for the operational amplifier. (See Paragraph 4 of this section for a more detailed description)

This feature permits the removal of the Pre-Patch Panel to balance the operational amplifier. However, when the computer is switched from POT SET to any other mode, the relay contacts open and the circuits as patched on the Pre-Patch Panel provides the feedback loop. Momentary amplifier overload may result during the relay operating time; thus to eliminate possible error in the computer solution, the operator should always switch the computer RESET (depress the RESET button) or ALL RESET (depress ALL RESET button for multi-mode operation only), before switching to the COMPUTE or REP OP mode. This permit the pot set relays to open and the amplifier summing junctions to settle before starting the problem solution. There is no actural waiting period required; that is, the operator may depress the RESET or ALL RESET button and then immediately depress the button for the desired mode. This sequence of operation will prevent the possible momentary overload from effecting the problem solution.

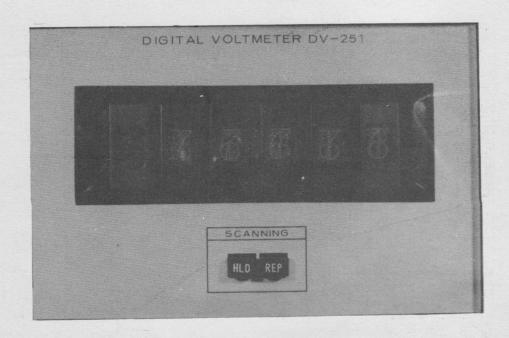

# b. Pre-Patch Panel Insertion and Removal

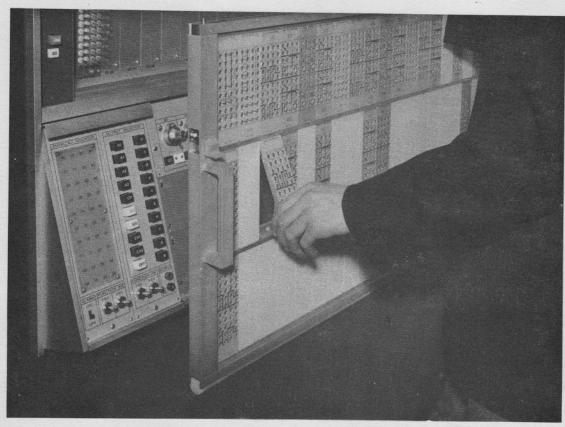

To insert the Pre-Patch Panel, set the lip on the lower edge of the panel in the quide groove (Figure 2.2-3). Push the top of the panel in so the panel is vertical until the panel is clamped automatically.

Depress the ENG (for ENGAGE) button on the lower left edge of the computing console. This button properly seats and firmly holds the Pre-Patch Panel in position. As the ENG and DIS (for DISENGAGE) buttons can memorize the operator action, it is not necessary to keep the button depressed until the panel is loaded. In the ENG state, after the panel is loaded, the panel can not be removed unless the DIS button is pushed.

FIGURE 2.2-3 PRE-PATCH PANEL INSERTION

In the ENG state without the panel, the panel can not be loaded. This feature eliminates the possibility of accidentally engaging or disengaging the Pre-Patch Panel.

The removal of the Pre-Patch Panel is essentially the opposite of inserting the panel. Depress the DIS button, and depress the levers on both handle of the panel. Then pull the panel towards the operator upper edge of the panel first.

It is not necessary to keep the panel straight by hand after inserting the panel or after pushing the DIS button.

#### c. Amplifier Balance

The d-c operational amplifiers are chopper stabilized to prevent drift and resultant errors in the computer results. Drift in an amplifier results in an output voltage (or offset) with a zero input. To eliminate offset, the amplifiers of the 505 are balanced, i.e., with a bias current is applied to the amplifier summing junction equal and opposite to any current due to drift thus placing the summing junction at virtual ground. Once balanced, drift in the amplifiers is eliminated automatically by the stabilizer circuit.

The d-c amplifiers of the 505 are extremely stable and normally do not require balancing for periods up to several months. To assure accuracy and confidence in the computer results, it may be desirable to check the amplifier balance daily; this check can be made rapidly and simply since the selector system and voltmeter are used.

There are two types of amplifier balance in the 505; the voltage balance check and current balance check. Usually, only voltage balance check will be sufficient for each amplifier. The current balance check is necessary to reduce integrator drift, but the operator need not check

it as a daily routine, because current drift is very low and stable.

The following is a step by step procedure for checking amplifier balance.

- (1) Place the voltmeter RANGE switch in the (plus or minus)

- O.1 position and depress the DIS button of the Pre-Patch Panel control switch. In this state the computer is ready for voltage balance check (BC mode).

- (2) Using the selector system, select each amplifier AOO through A39. The voltmeter should register a zero deflection for any other. Two positions of +0.1 and -0.1 of the voltmeter range switch will detect null error in the voltmeter.

- (3) Should an amplifier cause a deflection to either side of the center zero on the voltmeter, adjust the corresponding balance control. The balance control for amplifiers AOO through A39 (the operational amplifiers) are located directly behind the Pre-Patch Panel (Figure 2.2-4). There are two balance controls in an amplifier. They are voltage balance control and current balance control. In the BC mode (when DIS button pushed), only the voltage balance is necessary. Adjust these controls for a zero reading on the meter. The current balance should be done for integrator connection amplifiers in HOLD mode.

#### d. Changing Computational Components

In the solution of some problems it may be necessary to add a specific type of computational component to the existing complement. Since many of the module positions are designed to handle more than one type of computing component, a component not required in the problem investigation may be removed and another unit placed in that cradle.

FIGURE 2.2-4 AMPLIFIER BALANCE CONTROL LOCATION

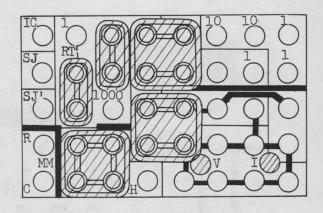

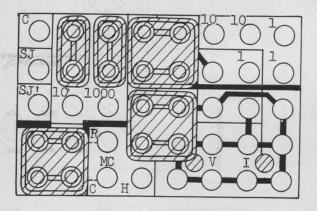

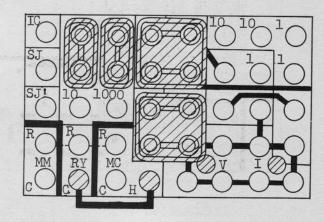

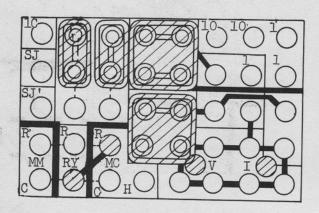

|      | (A)          | A12   | A13  | 4           | A26  | A27 | (E4)        |       |     |             |                    |                    |                 |               |                                   |            |

|------|--------------|-------|------|-------------|------|-----|-------------|-------|-----|-------------|--------------------|--------------------|-----------------|---------------|-----------------------------------|------------|

|      | 0            | (Z)   |      | 0           | R    |     | (A)         |       |     |             | etc.               |                    |                 |               |                                   |            |

| 5    | A            | Alo   | A11  | A           | A24  | A25 | A           | A 38  | A39 | 2           | EM-151,            | AO-151             | PI-151          | 00-151        | FS-151                            | TR-151     |

| 7    | EA 3         | 0     |      | AREA 6      | 0    |     | N 9         | (fz4) |     | 4           |                    |                    | 五               | 8             | 꿆                                 | II         |

| 3    | LE AREA  (A) | A08   | 409  | 1 1 -       | A22  | A23 | MODULE AREA | A36   | A37 | 2           | NON-LINEAR ELEMENT | AUTOMATIC OPERATOR | ន្ល             |               | СН                                |            |

| N    | MODULE       |       |      | MODULE      |      |     | MODUL       |       |     | 2           | AR EL              | E 0PE              | METER           | PANET         | I SWIT                            |            |

| Н    | PH           | P12   | P1.7 | (A)         | P30  | P35 | (P)         | P48   | P53 | 7           | -LINE              | OMATI              | POTENT IOMETERS | READOUT PANEL | FUNCTION SWITCH                   | TRUNKS     |

| 2    | A            | A06   | A07  | A           | A20  | AZI | A           | A34   | A35 | 2           | 1                  | -                  | -               | -             | 0                                 | _          |

| 4    | AREA 2       | (F4)  |      | TA 5        | (F4) |     | S N         | (f±4) |     | 4           | (N)                | 0)(0)              | ) (A            | ) (H          | (v)                               | (FH)       |

| 3    | (-1)         | A04   | A06  | MODULE AREA | A18  | 419 | E AREA      | A32   | A33 | m           |                    | CP-151 OR CP-152   |                 |               |                                   |            |

| 2    | MODULE       |       |      | MODUL       |      |     | MODULE      |       |     | 2           | Н                  | 1 OR               | 1               | П             | <b>т</b> д                        | -          |

| Н    | (A)          | P06   | PII  | (A4)        | P24  | P28 | (A)         | P42   | P47 | Н           | DA-151             | CP-15              | FD-151          | FG-151        | TD-151<br>TD-151                  | MC-151     |

| 5    | A            | A02   | A03  | A           | A16  | A17 | A           | A30   | A31 | 2           |                    |                    |                 |               |                                   |            |

| 4    | A N          | 0     |      | 4 N         | 0    |     | N Z         | 0     |     | 4           | PLIFI              | RATOR              | ξ               | Ü             | RATOR                             | OLLER      |

| 3    | E AREA       | A00   | AOL  | A AREA      | A14  | A15 | E AREA      | A28   | A29 | 2           | DC AMPLIFIER       | COMPARATOR         | DIODES          | ABLE FG       | DUAL INTEGRATOR<br>TRANSFER DELAY | CONTROLLER |

| N    |              |       |      | MODULE      |      |     | MODULE      |       |     | N           | DUAL               | QUAD               | FREE            | VARIA         | rn                                | MODE       |

| П    | (24)         | P00 - | P05  | (A)         | P18  | P23 | (A)         | P36   | P41 |             | A                  | 0                  | <u>a</u>        | (Fe4)         | 0                                 | M          |

| SLOT | (kt)         |       |      | (0)         |      |     | Œ           |       |     | SYMBOT, KEY |                    |                    |                 |               |                                   |            |

|      |              |       |      |             |      |     |             |       |     | SYMB        | Cition             |                    |                 |               |                                   |            |

FIGURE 2.2-5 COMPUTER COMPONENT MODULE ASSIGNMENT AREAS

Figure 2.2-5 illustrates the various positions of the computing components in the 505 module area. This diagram illustrates which type of computing component is compatible with each cradle or module position. The procedure for replacing a computer component and changing the Pre-Patch Panel patching block is described in the following Sub-Paragraphs (1) and (2).

#### NOTE

Failure to change the Pre-Patch Panel patching block may prevent proper use of a computer component due to the arrangement of jumpers on the rear of the patching block.

## (1) Computing Module Replacement

- (a) Remove the Pre-Patch Panel to expose the component modules, Remove the two phillips-head retaining screws from the top and bottom of the module to be removed. (Figure 2.2-6)

- (b) Insert the special module removal handle in the holes provided next to screw holes from which the screws were removed.

Attach the two screw knobs on the handle tightly. Pull the module forward removing it from the 505 console.

- (c) Place the new component in place. It is easier to insert the new module, if the handle is attached on the front of it.

Be sure the guide pin is properly seated in the guide rail before mating the connectors at the rear of the module.

FIGURE 2.2-6 REMOVAL OF COMPUTING MODULE

FIGURE 2.2-7 PATCHING BLOCK REPLACEMENT

(d) Check that the module is properly installed (connector firmly mated, etc.) and replace the two retaining screws.

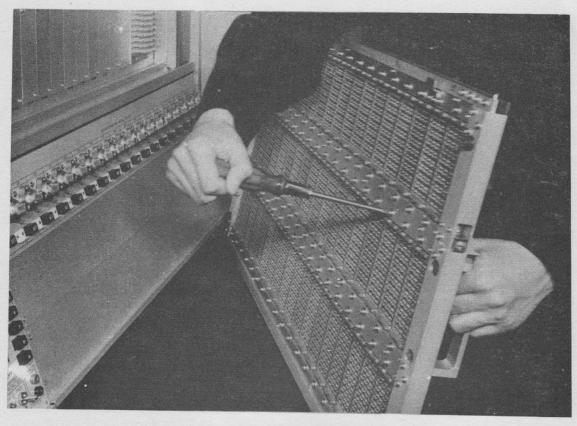

### (2) Patching Block Replacement

- (a) The Patching blocks of the computing components are held securely in place by the retaining screws on the rear of the Pre-Patch Panel (Figure 2.2-7)

- (b) The retaining screws are located on both ends of the patching block. Release them with a screw driver.

- (c) Once the retaining strip is free, remove the original block and replace it with the new block. Replace the two retaining screws. The Pre-Panel is now ready for problem patching.

#### 3. MONITORING AND CONTROL

The control system of the HITACHI 505 is designed to allow simple control and monitoring of the computer components (Figure 2.3-1). The following sub-paragraph describes the function and operation of the various monitoring and control facilities of the 505.

#### a. Output Selector SL-251

The output selector mainly consists of two rows of pushbuttons; The first row contains 4 buttons designated AO through A3, and the second row contains 10 buttons designated 0 through 9. Depressing the AO button permits the operator to select the outputs of the 10 operational amplifiers (AOO through AO9). In the same way, depressing the CP button in the first row permits

FIGURE 2.3-1 HITACHI 505 CONTROL AREA

the operator to select the outputs of the comparators (ordinally CPO through CP8).

The two reference voltages are selected only by pushing the buttons designated 100 (red, for positive) or 100 (blue, for negative), nevertheless any button of the second row depressed. The button designated EX1 permit the operator to call an external signal from an external device, for instance the output selector in the additional computing console CS-505A. A button designated EX2 has no connection and is provided as a spare selector.

Depressing the button, one of AO through A3, sets the selector system for amplifiers in a given tens group, i.e., if the

button designated Al is depressed, amplifiers AlO through Al9 are

set up for selection. The button in the second row designates which

of these ten amplifiers is actually selected. The selector system

button numbering corresponds with the amplifier and comparator

designations as marked on the Pre-Patch Panel respectively.

The selector system output is connected to the ten terminations marked SEL in the upper portion of the Readout Panel OC-151 (Figure 2.3-1)

In order to read out a selected signal on the DVM, the left bottle plug shown in Figure 2.2-2 must be in place. The multi-range voltmeter (VM) may also be connected to the selector line by installing the correct bottle plug shown in the illustration. It should be noted, however, that the VM circuit will load the output of the selected component with a relatively low impedance and should not be used if the circuit cannot tolerate this load. If the operator requires setting the potentiometer or reading the voltage

accurately, use the voltmeter as a nullmeter utilizing the reference potentiometer as a standard voltage divider.

# b. Overload Indicator OL-251

The overload indicators (Figure 2.3-1) provide a visual alarm when an overload occurs in any of the operational amplifiers, i.e., when the summing junction is not at virtual ground. An overload may be due to improper scaling, improper patching or loading.

When the computer is initially turned on, all the indicator lamps may light; however, in a few seconds, as the amplifiers settle, all the lamps should go out. Should a lamp remain lit it could be a patching error such as the failure to provide un-used amplifiers with feed-back (via the four or six connector bottle plugs). Prolonged overload will not damage an amplifier.

To eliminate the audible signal in the initial overload, it is recommended to turn off the switch designated ALARM on the panel.

# c. Digital Voltmeter DV-251

The digital voltmeter (DVM) DV-251 is terminated in the Readout Panel OC-151 area (Figure 2.3-2) and is designated DV. As previously mentioned the DV may be bottled to the SEL termination to monitor the selector system voltages, or with a patch cord the digital voltmeter may be used to monitor signal levels at practically any termination in the Pre-Patch Panel. The DVM has a 50 megohm (minimum) full-time input impedance.

It will take about 30 minute warm up time to operate the digital voltmeter in the specified accuracy for the measurement of an absolute voltage. For the analog computer, it is not necessary to obtain the absolute voltage, so the operator may use the digital voltmeter

FIGURE 2.3-2 READOUT PANEL OC-151 PATCHING BLOCK AND DVM/VM TO SEL PATCHING

approximately 10 minutes after the power has been switched on.

(d) Multi-Range Voltmeter (in Control Panel CT-251)

The multi-range voltmeter is permanently wired into various circuits of the 505 to facilitate rapid readout of certain voltages by automatic switching synchronized to MODE control. The voltmeter has a RANGE switch, thus permitting close to full scale readouts for maximum accuracy. The ranges are 0.1,-0.1, 1, 10, 30, 100 and 300 volts (in addition to an off position).

In the ENG state of the Pre-Patch Panel driving switch, the RANGE switch is connected to the Pre-Patch Panel VM termination (Figure 2.3-2) permitting this point to be bottle-plugged to the SEL output or, as in the case of the digital voltmeter, monitoring voltages at most Pre-Patch Panel terminations via a patch cord.

Following is a list of the voltmeter connections in each mode of operation with a brief description.

MODE DESCRIPTION

BC (DIS) Connects the amplifier output addressed by the selector system to the meter to facilitate checking and/or adjusting.

The amplifier balance, notwithstanding the con-

nection on the Pre-Patch Panel.

All modes Connects the meter to the VM Pre-Patch termina-except BC tion.

In each mode, the connection will be made via the RANGE switch.

If the NULL button in the REFERENCE POTENTIOMETER area is depressed, the voltmeter system with the RANGE switch can be used as a null meter referred to the reference potentiometer. The polarity of the reference voltage (plus or minus 100 volts) which will be applied to the reference potentiometer as a null meter may be decided by the toggle switch next to the NULL push button.

## e. Reference Potentiometer (in Control Panel CT-251)

The reference poteniometer on the control panel may be used in two ways; as an ordinary potentiometer and a null meter mentioned already.

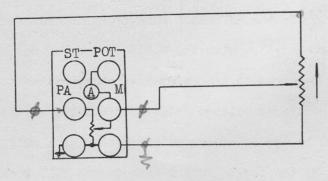

In the state that the NULL button is not depressed, the reference potentiometer may be used as an ordinary potentiometer terminated on the FUNCTION SW area of the Pre-Patch Panel (Figure 2.3-3).

In the state that the NULL button is pushed down, the reference potentiometer may be used as arms of the null meter. In this state, the reference voltage may be applied directly to the top end of the reference potentiometer. The polarity of the voltage is controlled by the toggle switch next to the NULL push button.

f. Mode Control (in control Panel CT-251)

The operating mode of the computer is controlled by the six pushbutton selector just to the above of the POWER button (Figure 2.3-1). Following is a list of the pushbutton and brief description of their functions.

(a) ORDINARY POTENTIOMETER CONNECTION (THE STATE NULL BUTTON UP)

(b) NULLMETER SYSTEM CONNECTION (THE STATE NULL BUTTON DOWN)

FIGURE 2.3-3 SIMPLIFIED SCHEMATIC OF REFERENCE POTENTIOMETER

MODE BUTTON

#### DESCRIPTION

RESET

In the RESET mode all circuits except the integrators function normally.

The integrator outputs are held at their respective initial conditions (IC) as dictated by the IC input voltage.

(The integrator output is zero if no IC voltage is applied)

COMPUTE

When this pushbutton is depressed, all integrators are simultaneously released to respond to input signal voltages. The integrator outputs change in potential as dictated by the inputs; a time varying behavior is produced. This generates the voltage solution of the programmed problem.

HOLD

Depressing the HOLD pushbutton permits the problem solution to be halted and all voltages held at the potential attained up to the instant of depressing the button. The problem may be continued from this point by depressing the COMPUTE button or re-set to the starting point by depressing the RESET button.

MODE BUTTON

DESCRIPTION

POT SET

Amplifier input resistor summing junction grounded; permits setting potentiometers under actual load. Also provides amplifiers with relay-contact feedback in order that Panel may be removed to balance amplifiers.

ALL RESET

In the ALL RESET mode all circuits except integrators function normally. All integrator outputs are held at their respective initial conditions (IC), regardless the connection of the Integrator driving circuits. This mode may be used especially in separate mode control operation.

REP OP

The REP OP button switches the computer into the repetitive operation mode if the oscilloscope OS-251 or the timer (TM-251 or TM-253) is provided in the 505. In this mode the each of the integrator capacitor will change to the capacitor connected to the terminal designated RO on the integrator area of the Pre-Patch Panel, if the INTEGRATOR CAPACITOR switch on the control panel is located on RO position.

If the switch is turned to the RT position, the integrator capacitor connection remains at the terminal designated RT on the integrator area of the Pre-Patch Panel.

The latter state will be many useful to operate the

MODE BUTTON

#### DISCRIPTION

REP OP (Continued)

computer in low speed (Real Time) repetitive or iterative computation.

The following table shows the operation in each state simply.

| MODE<br>BUTTON                  | INTEGRATOR<br>CAPACITOR SWITCH | ACTUAL INTEGRATOR<br>CAPACITOR CONNECTION |

|---------------------------------|--------------------------------|-------------------------------------------|

| REP OP                          | RO                             | RO                                        |

|                                 | RT                             | RT                                        |

| EXCEPT REP<br>OP<br>MANUAL COMP | RO                             | ORT ?                                     |

|                                 | RT Care                        | RT                                        |

### g. Trunks

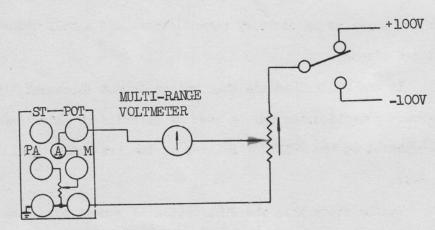

There are two types of trunks; Pre-Patch Panel trunks and control trunks. Pre-Patch Panel trunks (terminating at the TRUNKS TR-151 area) provide point-to-point connections to the connectors at the right-rear of the computer (Figure 2.3-4). These connectors may be used as outputs to accessory equipment, or the trunk terminations may be cabled to a second computing console, CS-505A, as signal carrying lines for the interconnection of the problems patched on separate Pre-Patch Panels of slaved computing consoles.

Control trunks (terminating at the Readout Panel OC-151 area) provide point-to-point connections to the Control Panel CT-251. These connectors may be used as input/output channels

or the temporary connectors to the test equipment.

Slave switches (in Control Panel CT-251)

When a 505 is to be slaved to another 505 (master), the button EXT of the SLAVE area in the Control Panel is depressed. The slaved computer then responds to the selected modes of the master computer pushbuttons.

When a 505 is to be controlled by the Digital Element

Panel or the Timer, the button INT of the SLAVE area is de

pressed. Then, the computer is driven with signals from input

of the analog patchboard or the digital patchboard. For normal

manual operation, the OFF button of the SLAVE area should be

kept down.

FIGURE 2.3-4 CONNECTING AREA, REAR THE COMPUTING CONSOLE CS-505A

#### i. Readout Devices

The problem solution obtained from the 505 may be permanently recorded or temporarily displayed on various types of readout devices. A few of the more common readout devices are described in this paragraph.

Either the DVM or voltmeter may be used to read out the problem solution. These devices, however, do not record the solution and thus do not provide a permanent record. When in REP-OP the computer solution may be obtained by photographing the scope trace. X-Y recorders or strip-chart recorders may be used for permanent record of 505 problem solutions. These units, however, do not have the frequency response necessary to accurately record the solution when the computer is placed in the high-speed REP-OP mode of operation. The recorder terminations on the Readout Panel are wired to connector plugs at the rear of the 505. See Figure 2.3-4.

Oscilloscope OS-251 is especially prepared for the exhibition of the computer solution. The OS-251 has three channel inputs and can be mounted on the Control Console CS-505B. All input terminals are connected on the Readout Panel OC-151 area in the Patchboard.

### j. Function Switches

The Function Switches (on the Overload Indicator OL-251 and Output Selector SL-251, 4 switches total) provide 3-position single-pole (FSO, FS1) and double-pole(FS2, FS3) contacts. They are terminated on the Function Switch FS-151 area of the patchboard. With these switches the operator may manually switch computer problem functions. The center position may be considered the off position.

### k. Power Switches (in Control Panel CT-251)

The AC power to operate the computer is controlled by the POWER switches on the Control Panel CT-251. When the AC cord is connected from an external AC source to the Power Supply, the OFF switch will light and notify the operator that AC power is ready, the Oven in the computing console is working and Pre-Patch Panel driving mechanism is ready to actuate.

When ON switch is pushed, the Power Supply PS-051 will furnish all the DC, AC and square-wave power necessary to operate the whole computer.

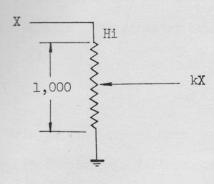

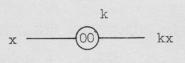

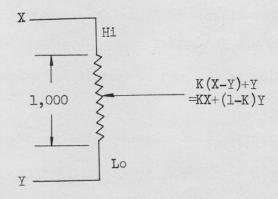

### 4. POTENTIOMETERS

One of the simplest and most useful operations performed on an analog computer is the multiplication of a variable voltage by a signal. The Hitachi 505 has a basic complement 18 potentiometers and may be expanded to a full complement of 54 potentiometers.

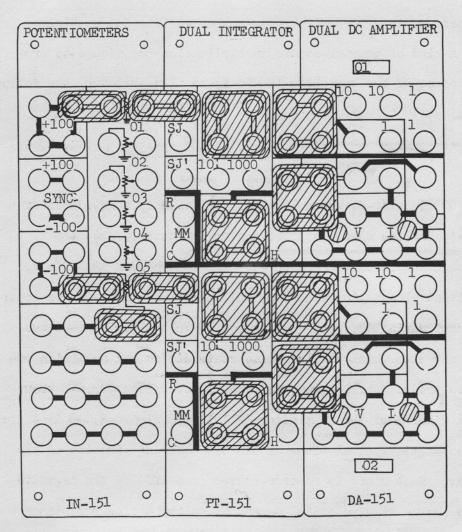

Each Potentiometer Panel PT-251 provides 18 potentiometers for setting problem coefficients, initial conditions, and problem inputs. The potentiometers are mounted to a maximum of 3 horizontal rows of 18 potentiometers per row. Each row is terminated at a corresponding row of the Pre-Patch Panel; three modules PT-151 of a row in the Pre-Patch Panel terminate a Potentiometer Panel PT-251. Each Potentiometer Patch Module PT-151 contains 6 potentiometer terminals. Five of the six poteniometers have one end grounded while the sixth has both ends ungrounded. (See Figure 2.4-1)

The standard potentiometers in the 505 are 10 turn, wirewound, 30K ohms, individually fused units with calibrated dials and a locking mechanism.

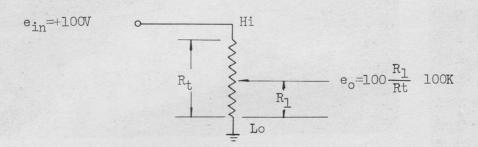

The potentiometer may be used in conjunction with reference to obtain a fixed accurate voltage less than reference, or to multiply a problem variable by any constant less than unity. Figure 2.4-1 is a schematic of a potentiometer with +100 volts applied to the high end\*, where K is;

$$K = \frac{R_1}{R_t}$$

(EQ.2.4-1)

The potentiometer shown in Figure 2.4-5 is unloaded, and the mechanical ratio of R<sub>1</sub>:R<sub>t</sub> equals the electrical ratio e<sub>0</sub>:e<sub>in</sub>; thus, the potentiometer may be set to the exact ratio by means of the calibrated dial attached to the wiper shaft. However, the two ratios will not be equal when the potentiometer is loaded as is the case when it is used as a computer problem element. Normally, the pot is loaded by either a 1M or 100K ohm resistor since a potentiometer generally feeds an amplifier and these values are the most common amplifier input resistors. Figure 2.4-3 illustrates the effect on the e<sub>in</sub>:e<sub>0</sub> and R<sub>1</sub>:R<sub>t</sub> ratios when the potentiometer wiper feeds a 100K load.

In order to eleminate the effects of loading, it is more convenient to set the poteniometers under actual load and monitor the wiper voltage

<sup>\*</sup> The high end of a potentiometer refers to the termination of the Prelocated at the top of the schematic designation of the Pre-Patch Panel. The low end is the bottom termination, normally grounded except in the case of the ungrounded potentiometer.

FUSE LOCATION (REAR OF POTENTIOMETER PANEL)

PATCHING UNIT

POTENTIOMETER PANEL

FIGURE 2.4-1 POTENTIOMETER PATCHING UNIT PT-151 AND POTENTIOMETER PANEL PT-251

FIGURE 2.4-2 POTENTIOMETER SCHEMATIC SHOWING ein TO eo RELATIONSHIP FOR ein=100 VOLTS

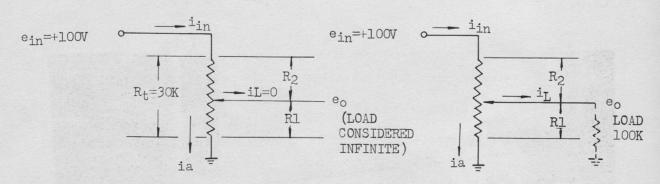

- (a) INFINITE LOAD: DIAL SET AT 0.33 (b) look LOAD: DIAL SET AT 0.

:. e<sub>o</sub> =100-3.33(5)=83.3 VOLTS  $\frac{R_1}{R_{t}} = 0.833$  (AS SET BY DIAL)

$$\frac{e_0}{e_{in}} = \frac{83.3}{100} = 0.833$$

$$\frac{R_1}{R_t} = \frac{e_0}{e_{in}}$$

(a) INFINITE LOAD: DIAL SET AT 0.833 (b) 100K LOAD: DIAL SET AT 0.833

$$\therefore R_1 = 25K \qquad R_2 = 5K$$

$$e_0 = 100 - i_{in} R_2$$

$$i_{in} = i_L + i_a$$

WITH 100K LOAD iin=4.00 ma.

e<sub>o</sub> =100-4.00(5)=80.0 VOLTS

$$\frac{R_1}{R_t} \neq e_o$$

FIGURE 2.4-3 POTENTIOMETER LOADING

(The potentiometer output), than to calculate a corrected mechanical ratio (R1:Rt).

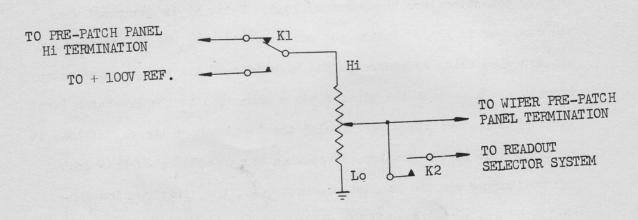

Figure 2.4-4 illustrates the 505 circuitry provided to permit setting the potentiometers under actual load. Relay Kl is energized when the computer is placed in the pot set mode (depress POT SET button) and applies +100 volts reference to the high ends of all the grounded potentiometers. Note that the wiper remains connected to the Pre-Patch Panel termination; thus, the wiper "feels" the impedance of the actual load it is patched to in the problem. Even when the potentiometer is selected for monitoring via the readout pushbutton Kl, the wiper remains connected to its actual load. The readout pushbutton connects the wiper to a high impedance DVM or, in the absence of the DVM, a null pot circuit. The operator may then set the wiper for the attenuation factor required in the problem.

The method of the setting the ungrounded potentiometers is quite similar to the setting the grounded ones. The low ends are transfered from the Pre-Patch Panel terminals to ground in the pot set mode.

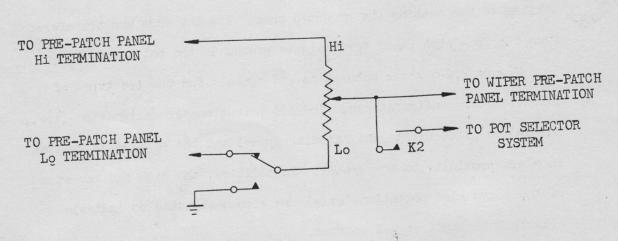

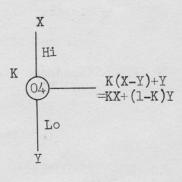

Figure 2.4-5 shows schematics and symbols for the two types of potentiometer configurations. The 505 potentiometer designation (i.e., number) is given within the circular symbol and the setting is written in close proximity to the symbol. In addition, the high and low ends of the ungrounded potentiometer(s) are also designated to indicate clearly both input signal sources.

The neon lamp located at the left side of the each potentiometer will light when the potentiometer readout button just below the potentiometer is pushed, and notify the operator that this potentiometer connected to the readout system.

a. GROUNDED POTENTIOMETER CIRCUIT

b. UNGROUNDED POTENTIOMETER CIRCUIT

FIGURE 2.4-4 505 POTENTIOMETER CIRCUITS, SIMPLIFIED SHEMATIC

- a. GROUNDED POT SCHEMATIC

- . b. GROUNDED POT COMPUTER DIAGRAM SYMBOL

c. UNGROUNDED POT SCHEMATIC

d. UNGROUNDED POT COMPUTER DIAGRAM SYMBOL

NOTE:  $K=e_0/e_{in}$

FIGURE 2.4-5 POTENTIOMETER SCHEMATIC AND COMPUTER SYMBOLS

The potentiometer having a lower number has priority. When two buttons are pushed, the lower numbered potentiometer will be selected.

### 5. OPERATIONAL AMPLIFIER

### a. General Considerations

When a high-gain d-c amplifier is used in conjunction with input and feedback networks to perform mathematical operations, the resulting system is generally referred to as an operational amplifier. The operational amplifier is the basic and most versatile unit in the analog computer. It can be used for inversion, summation, multiplication by a constant, integration, and used in conjunction with special networks for squaring, extracting square root, generating logarithmic functions, etc.

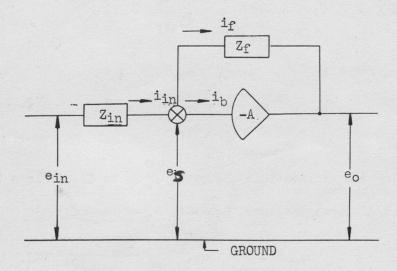

To understand the basic concept of the operational amplifier, consider the simplified block diagram of Figure 2.5-1 where a high-gain amplifier (gain of -A) has a feedback impedance Z<sub>f</sub> and an input impedance Zin. The amplifier is designed so that it has three basic and essential characteristics.

- (1) The amplifier output (e<sub>o</sub>) is related to the summing junction voltage (e<sub>s</sub>) by the gain of the amplifier:  $e_o = -Ae_s$

- (2) The input stage of the amplifier draws neglisible current: ib  $\approx$  0

- (3) The open loop gain of the amplifier is extremely high:  $A\gg 1$  (on the order of 107 at d-c).

Using Kirchhoff's laws, the nodal current equation at the summing junction (SJ) is:

or

$$\frac{e_{\text{in}} - e_{\text{s}}}{Z_{\text{in}}} = \frac{e_{\text{s}} - e_{\text{o}}}{Z_{\text{f}}} + i_{\text{b}} \quad \text{(EQ. 2.5-1)}$$

FIGURE 2.5-1 OPERATIONAL AMPLIFIER, SIMPLIFIED BLOCK DIAGRAM

since  $e_s = e_0/A$ , and since  $i_b \approx 0$ , Equation 2.5-1 can be rewritten to obtain:

$$\frac{e_{\text{in}}}{Z_{\text{in}}} + \frac{e_{\text{o}}}{AZ_{\text{in}}} = -\frac{e_{\text{o}}}{AZ_{\text{f}}} - \frac{e_{\text{o}}}{Z_{\text{f}}}$$

Solving for  $e_0$ :  $= \frac{-\frac{Z_f}{Z_{in}}}{1 + \frac{1}{A}\left(\frac{Z_f}{Z_{in}} + 1\right)}$ (EQ. 2.5-2)

In most applications the ratio of  $Z_{\hat{\mathbf{f}}}$  to  $Z_{\hat{\mathbf{in}}}$  is less than 30 and since 1/A approaches zero, Equation 2.5-2 becomes:

$$e_0 = -\frac{Z_f}{Z_{in}}$$

$e_{in}$  (EQ. 2.5-3)

Equation 2.5-3 illustrates one of the most important considerations of the operational amplifier:

The input output relationship of the operational amplifier is solely dependent on the ratio of the feedback to the input impedance.

Using Equation 2.5-3 as the basis of discussion, the following subparagraphs describe the various uses of the operational amplifier.

### (1) <u>Inversion</u>

When the same value resistor is used for both the feedback and the input impedance, the amplifier output voltage has the same amplitude as the input voltage but is opposite in polarity.

$$e_0 = -\frac{R_f}{R_{in}} e_{in}$$

In the 505, the value of  $R_{

m f}$  and  $R_{

m i}$  used for the inverter is normally 1M ohms, therefore:

$$e_0 = -\frac{1M}{1M}$$

$e_{in} = -e_{in}$

Thus a +100 volt input results in a -100 volt output, and the amplifier is said to have a gain of minus one. The accuracy of the output to input ratio depends solely on the accuracy of the ratio  $R_f/R_{\rm in}$ .

(2) Multiplication by a Constant A change in the ratio of the resistors results in multiplication by a constant. With  $R_{\mathbf{f}}$  equal to 1M and  $R_{\mathbf{in}}$  equal to 100K for example, the amplifier output is:

$$e_0 = -\frac{1M}{100K} e_{in} = -10 e_{in}$$

An input of plus 10 volts results in an output of minus a hundred volts. This operational amplifier has a gain of ten.

The multiplying constant can be made less than one by using a 100K feedback resistor with a 1M input resistor.

$$e_0 = -\frac{100K}{1M}$$

$e_{in} = -0.1 e_{in}$

An input of minus 100 volts produces an output of 10 volts.

(3) Summation When multiple input resistors are used with a feedback resistor  $R_{\rm f}$ , the basic relationship is extended to:

$$e_0 = -\left(\frac{R_f}{R_1}e_1 + \frac{R_f}{R_2}e_2 + \dots + \frac{R_f}{R_n}e_n\right)$$

The circuit can be used to algebraically sum an indefinite number of inputs; furthermore, each input may be multiplied by an arbitrary constant.

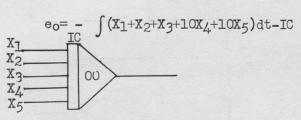

(4) Integration with Respect to Time When the feedback element Zf is a capacitor rather than a resistor the summing junction current equation is;

$$\frac{e_1}{R_1} + \frac{e_2}{R_2} + \dots + \frac{e_n}{R_n} = -C \frac{de_0}{dt}$$

Integrating this equation and assuming an initial charge on the feedback capacitor of Vo:

$$e_0 = -\frac{1}{C} \int_0^t \left( \frac{e_1}{R_1} + \frac{e_2}{R_2} + \dots + \frac{e_n}{R_n} \right) dt + Vo$$

Looking at this another way, if Zf is a capacitor having an operational impedance 1/pC and  $Z_{\rm in}$  is a resistor, the basic operational amplifier relationship, Equation 2.5-3 becomes

$$e_o = -\frac{E_{in}}{pRC} = -\frac{1}{RC} \int_0^t e_{in}dt$$

With this arrangement, the operational amplifier will integrate (with respect to time) any input voltage. In addition to integrating, the amplifier also inverts the input voltage. An indefinite number of input may be applied to produce the time integral of the sum of the input voltages.

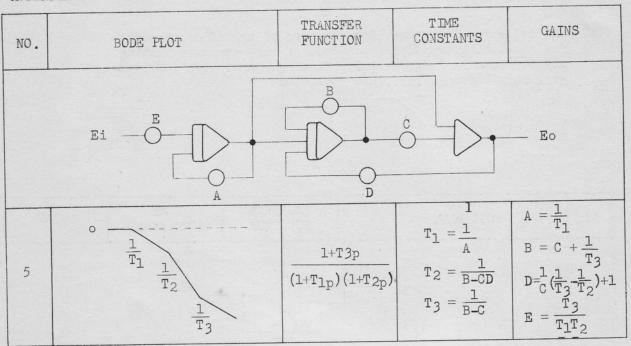

(5) Other Mathematical Operations As previously indicated the operational amplifier has uses other than those indicated in subparagraph (1) through (2). Complicated transfer functions can be simulated by using series and parallel RC networks for the feedback and input impedances. The circuit performance is still governed by the basic relationship of Equation 2.5-3. For the general case where three channel networks are used, the short circuit transfer impedance of Z<sub>f</sub> and Z<sub>in</sub> must be used. (The short circuit transfer impedance of a network is the ratio of input voltage to short-circuit output current.)

The input and feedback elements need not be linear; therefore, almost any non-linear characteristic can be approximated. The amplifier can also be used in conjunction with diodes and resistors to simulate the non-linear operations of limiting, dead-zone generation, X<sup>2</sup>, LogX, etc.

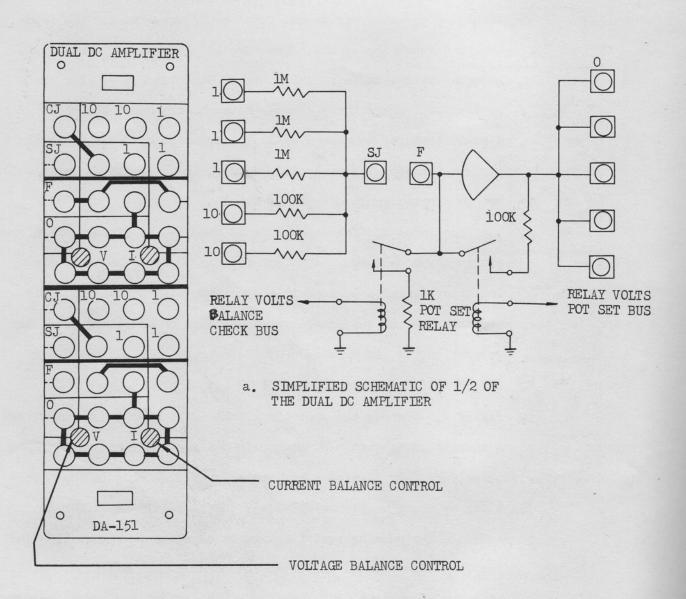

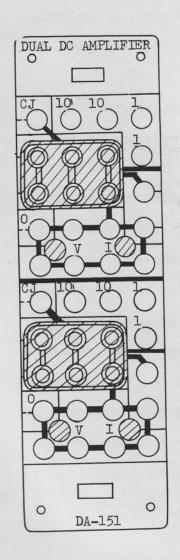

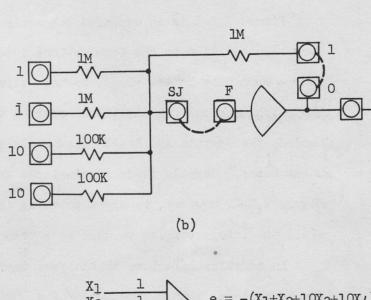

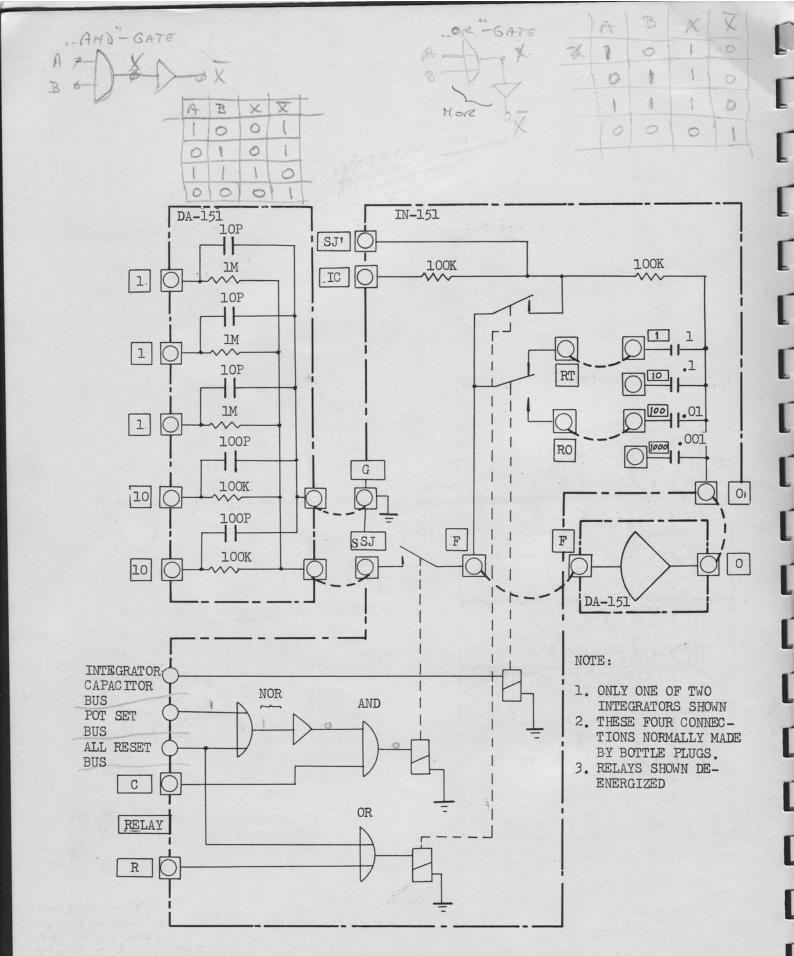

## b. 505 Operational Amplifier DA-151

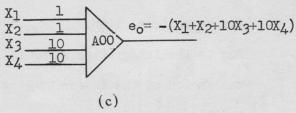

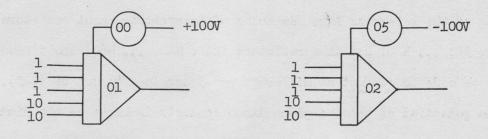

Figure 2.5-2 shows the operational amplifier patching terminations and a simplified schematic of high gain d-c amplifier and summing resistor network. By placing a six connector bottle plug in the patching block as shown in Figure 2.5-3(a), the high-gain amplifier is connected to the summing resistor network as shown in Figure 2.5-3(b). The resultant operational amplifier can be used for inversion, multiplication by a constant, and summation. The computer diagram symbol is shown in Figure 2.5-3(c). On the computer diagram it is customary to shown only those inputs that are used; the amplifier number is written inside the triangular symbol.

FIGURE 2.5-2 OPERATIONAL AMPLIFIER, SIMPLIFIED SCHEMATIC AND PATCHING BLOCK LAYOUT

NOTE: IF AMPLIFIER IS NOT USED, BOTTLE PLUG REQUIRED TO PROVIDE FEEDBACK.

(a)

FIGURE 2.5-3 SUMMER AMPLIFIER PATCHING

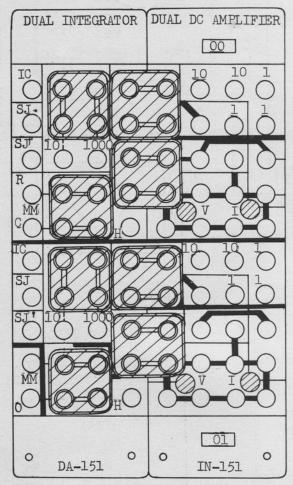

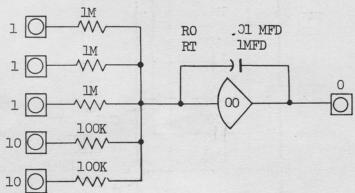

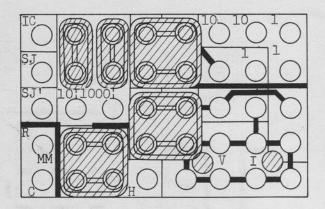

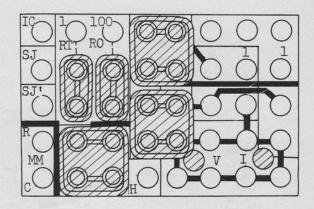

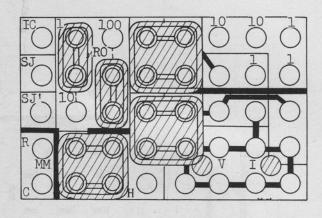

Figure 2.5-4(a) shows the patching to provide an operational amplifier that is capable of integrating with respect to time.

Figure 2.5-4(b) illustrates a simplified schematic for an amplifier patched as an integrator. The computer symbol for an integrator is shown in Figure 2.5-4(c).

Figure 2.5-5 is an expanded schematic of the integrator amplifier. In addition to the terminations interconnected by the two four - connector bottle plugs, certain circuits are brought out to the patching block for additional control of the integrators. These include the Compute and Reset relay coils and the compute hold and reset buses. Normaly these terminations are connected as shown in Figure 2.5-4; however, by cross patching (hold bus to reset relay, etc.) the integrator can be used as a track and hold unit.

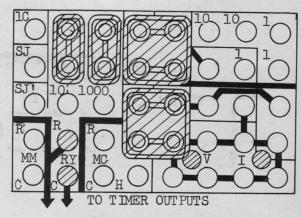

An additional feature is the free termination of four integrating capacitors; 1 uF, .1 uF, .01 uF and .001 uF. They are corresponding to the integrating gains of 1, 10, 100 and 1000. the operator has the choice of the integrating gain both in RT (real time operation) and RO (repetitive operation), connecting the selected capacitors to RT and RO terminals on the patch panel. The two holes designated R and C of the MM area of the Dual Integrator are the trunk lines to control the integrator mode by the digital logic elements which will be mounted on the Control Console CS-505B.

a. INTEGRATOR PATCHING

b. INTEGRATOR SIMPLIFIED SCHEMATIC

c. COMPUTER DIAGRAM SYMBOLS

NOTE: IF AMPLIFIER IS NOT USED, BOTTLE PLUG REQUIRED TO PROVIDE FEEDBACK.

FIGURE 2.5-4 INTEGRATOR PATCHING AND DIAGRAM

FIGURE 2.5-5 INTEGRATOR AMPLIFIER AND SIMPLIFIED SCHEMATIC

- 52 -

## 1. ORDINARY OPERATION (1)

INTEGRATING GAIN RT: 1

RO:100

INTEGRATING GAIN RT: 10

RO: 1000

## 2. ORDINARY OPERATION (2)

INTEGRATING GAIN RT: 1

RO: 1000

INTEGRATING GAIN RT: 10

RO:100

## 3. SPECIAL OPERATION (1)

MODE CONTROL BY MODE MATRIX IN DIGITAL LOGIC AREA

THE INTEGRATOR COMPUTES IN HOLD MODE

# 4. SPECIAL OPERATION (2)

THE INTEGRATOR COMPUTERS IN RESET MODE

THE INTEGRATOR IS CONTROLLED BY THE TIMER.

### 5. TYPICAL CONNECTION AROUND IN-151

THE PATCHING SHOWS TWO ORDINARY INTEGRATORS HAVING THE CIRCUITS BELOW.

IN REP OP MODE INTEGRATING GAIN IS MULTIPLIED BY 100.

## 6. QUARTER-SQUARE MULTIPLIER EM-151

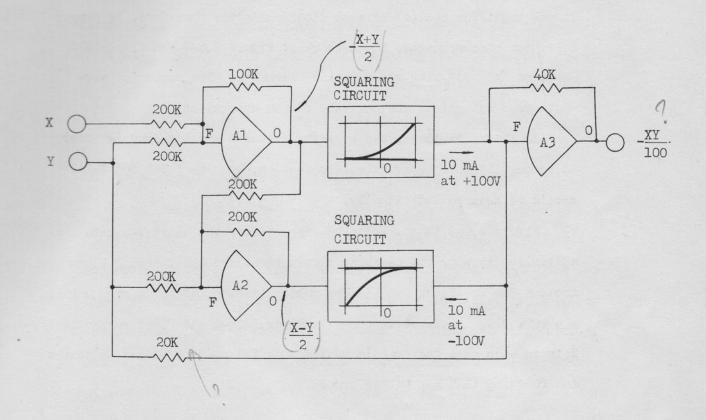

Multiplication of two variables is one of the non-linear operations necessary in a general purpose computer. The 505 Multiplier utilizes a kind of quarter-square multiplication techniques to produce a product of two variables (X and Y) as illustrated by the following equation:

$XY = \frac{1}{4} \left[ (X+Y+1)^2 - (X-Y+1)^2 - 4Y \right]$  (EQ. 2.6-1)

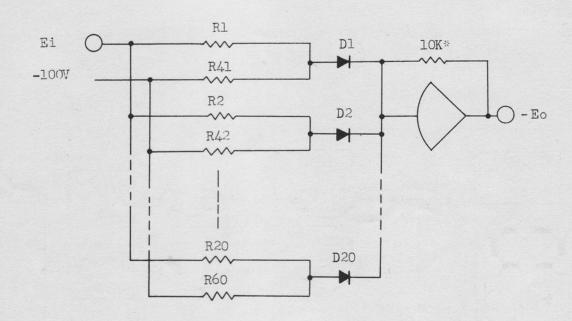

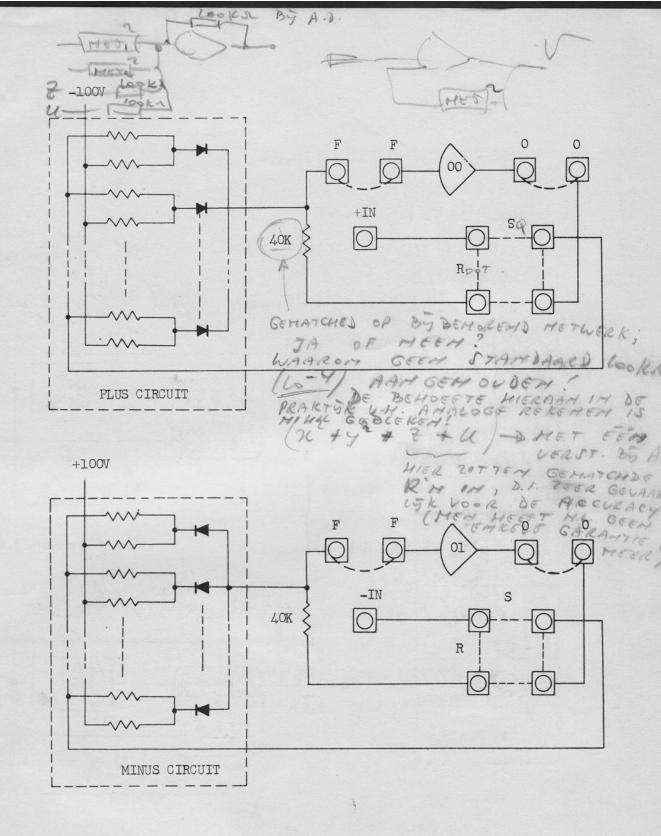

The 505 Quarter-Square Multiplier is basically a gated-resistor circuit application of the quarter-square technique. When the quarter-square multiplier is used with three high-gain amplifiers, the resultant circuit is capable of multiplication, division or squaring of input variables. The quarter-square multiplier employs two squaring circuits which utilize solid state diodes and precision resistors to produce the square of a given input. Figure 2.6-1 shows the block diagram of the Multiplier EM-151, and Figure 2.6-2 is a simplified schematic typical of one of the two squaring circuits of the multiplier. Each diode is reverse-biased (cut off) by the negative reference source at a potential dependent on the series resistance (R41, R42 ... R60) in the reference source leg. To cause a given diode to conduct, the sum of the X and Y input (applied via the summing amplifier) must attain a potential opposite in polarity and larger than the bias of the reference leg. By means of appropriate input resistors (R1, R2, ... R20) and bias resistors (R41, R42, ... R60) the diodes may be made to conduct at different pre-determined values of (X+Y). (The potential at which a given diode conducts is known as the diode breakpoint).

FIGURE 2.6-1 MULTIPLIER, SIMPLIFIED BLOCK DIAGRAM

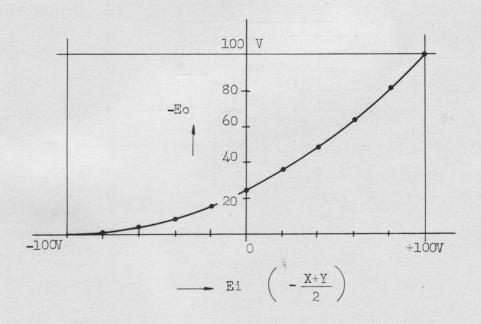

As the input (X + Y) reaches the breakpoint of each diode, the input resistors are essentially paralleled. The gain of the operational amplifier changes as each diode conducts; therefore, by proper selection of components, the network of Figure 2.6-2 can simulate a curve of  $(X + Y)^2$  with straight-line segments. The number of segments used determines the accuracy of the approximation.

In 505 Multipliers, two squaring circuits are required in order to accomplish four quadrant multiplication, because X+Y+1 and X-Y+1 should be squared individually.

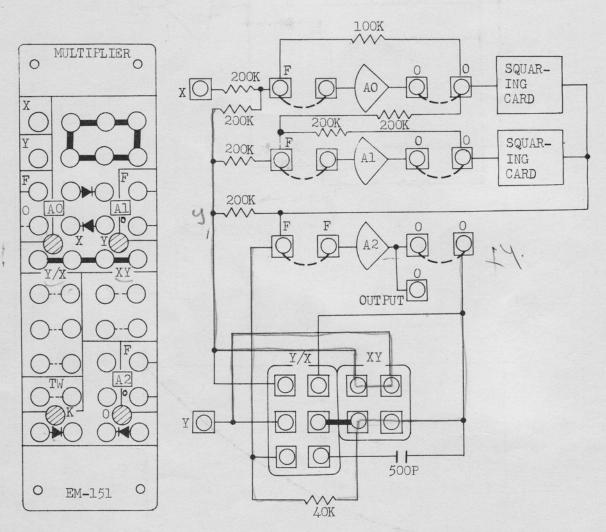

Figure 2.6-3 is a simplified schematic of the quarter-square multiplier showing the patching terminations and the patching block area of the Pre-Patch Panel. For multiplication, division or squaring, a bottle plug is placed as shown in Figure 2.6-4 and 2.6-5 respectively. Note in each case the symbols of the area the plug to placed indicates the function that may be performed.

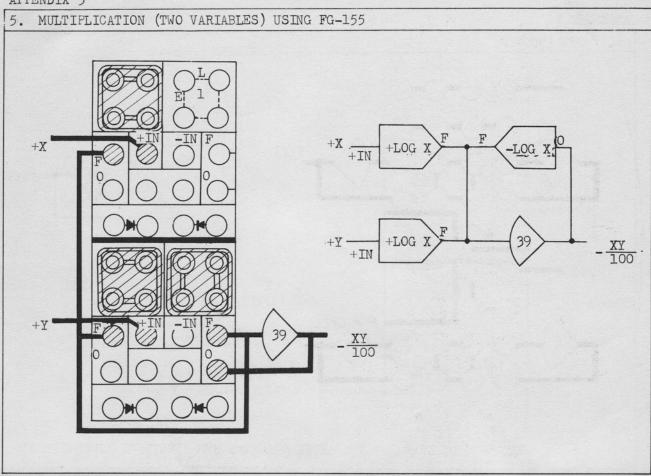

#### a. Multiplication

Figure 2.6-4 illustrates the patching procedure for multiplication of two variables, X and Y. Two inputs (X and Y) are necessary notwithstanding the polarity.

Note that the output voltage from the third amplifier is -XY/100 due to the inversion of the amplifier.

\* 40K IN MULTIPLIER

FIGURE 2.6-2 SQUARING CIRCUIT SIMPLIFIED SCHEMATIC

NOTE: AMPLIFIERS ARE NOT INCLUDED IN MULTIPLIER NETWORK EM-151

FIGURE 2.6-3 MULTIPLIER, SIMPLIFIED BLOCK DIAGRAM AND PATCHING BLOCK LAYOUT

TERMINALS "TW" SHOULD BE CONNECTED TOGETHER

IF DITHER SMOOTHING IS NECESSARY.

FIGURE 2.6-4 MULTIPLICATION PATCHING AND SIMPLIFIED SCHEMATIC

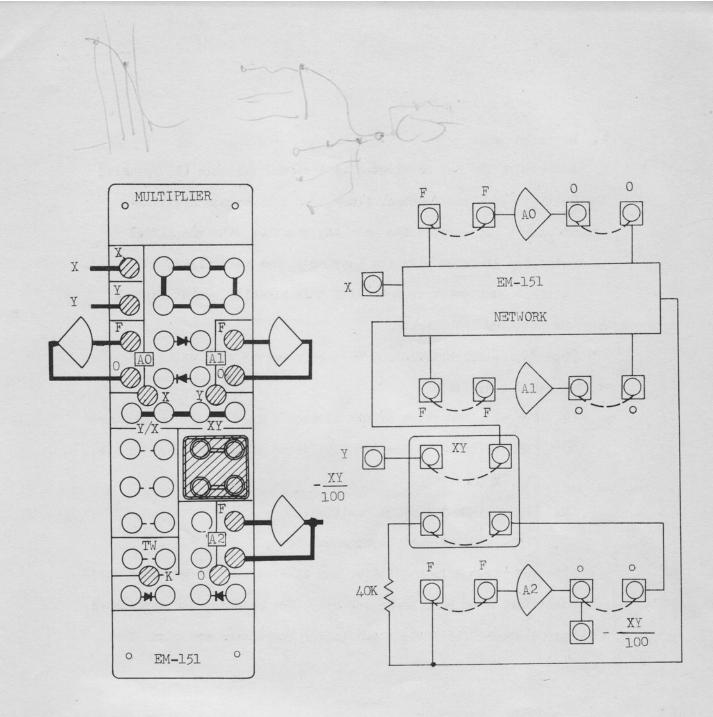

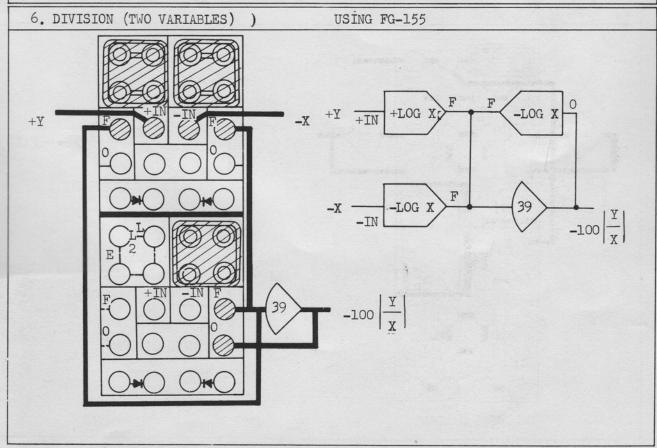

#### b. Division

A variable (Y) may be divided by a second variable (X) by using the multiplier as the feedback element of a high-gain amplifier.

Figure 2.6-5 illustrates the patching together with simplified schematic for division with the quarter-square multiplier.

An important point to note with this circuit is that input  ${\bf X}$  must be positive in polarity.

The following restrictions must be observed when using the multiplier for division.

- 1. The absolute value of the divisor X must always be greater than or equal to the absolute value of the dividend Y; i.e.,  $|Y|/|X| \leq 1.$

- 2. The divisor X must be positive.

- 3. The divisor X must never equal zero.

The quarter-square multiplier may also be used to generate various other functions such as  $X^2$  and etc. The patching and associated computer diagrams for various multiplier operations are given in Appendix 3.

NOTES: 1. X > Y

2. X > 0 3. X MUST BE POSITIVE

FIGURE 2.6-5 DIVISION PATCHING AND SIMPLIFIED SCHEMATIC

#### 7. FUNCTION GENERATORS

Six function generators are available for the 505. Three are of the fixed function type ( $X^2$ , log X and sin or cos X), and three kinds of variable function type (VFG), may be set to represent a single-valued function. All of the fixed function generators (FFG) operate on a principle similar to the quarter-square multiplier; i.e., diode gates are reverse biased such that the input voltage must attain certain levels to cause succeeding diodes to conduct. As each diode conducts the  $Z_f/Z_{in}$  ratio of the operational amplifier is changed.

On the other hand, VFG's operate on quite a different principle to the above; i.e., a transistor is adopted instead of a diode, and supplies a suturation curve instead of a single break point. It gives an a operator a simple way to set up a function.

### a. X2 Fixed Function Generator FG-154 A

The 505  $X^2$  FG accept both positive and negative input voltages and generates either a  $+X^2$  or a  $-X^2$  output. Figure 2.7-1 is a simplified schematic of the  $X^2$  generator circuit showing the high-gain amplifiers as normally patched into the circuits. To generate a  $-X^2$  function a four-connector bottle plug must be placed as shown in Figure 2.7-2(b); i.e., the two upper terminations are connected to ether as are the two lower terminations. For  $+X^2$  the connections should be made as shown in Figure 2.7-2(c).

Additional functions such as  $\sqrt{X}$  are also obtainable with the  $X^2$  FG. The patching and computer diagrams are given in Appendix 4.

FIGURE 2.7-1 X2 FG SIMPLIFIED SCHEMATIC

TERMINAL "Tw" SHOULD BE CONNECTED TOGETHER IF DITHER SMOOTHING IS NECESSARY.

FIGURE 2.7-2 X<sup>2</sup> FG SIMPLIFIED SHCEMATIC AND PATCHING BLOCK

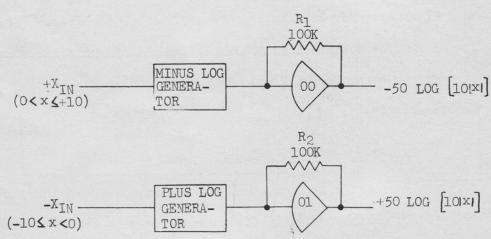

## b. Log X fixed Function Generator FG-155A

The 505 Log X FG contains four individual log function generators all of which are terminated at the Pre-Patch Panel. Two of the generators accept only positive voltage input and two accept only negative voltage inputs. The output of the generators is the scaled logarithm to the base 1 (i.e., 50 log. IXI).

Figure 2.7-3 illustrates the patching for both positive and negative voltage input log X generators. Additional patching and FFG uses (such as obtaining the antilog of a log input, multiplication, division, or raising an input to an unusual power) are given in Appendix 5.

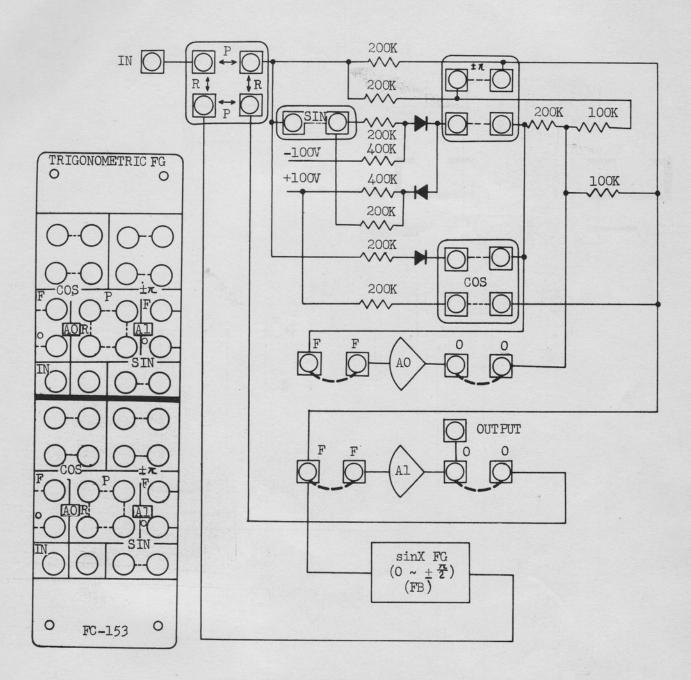

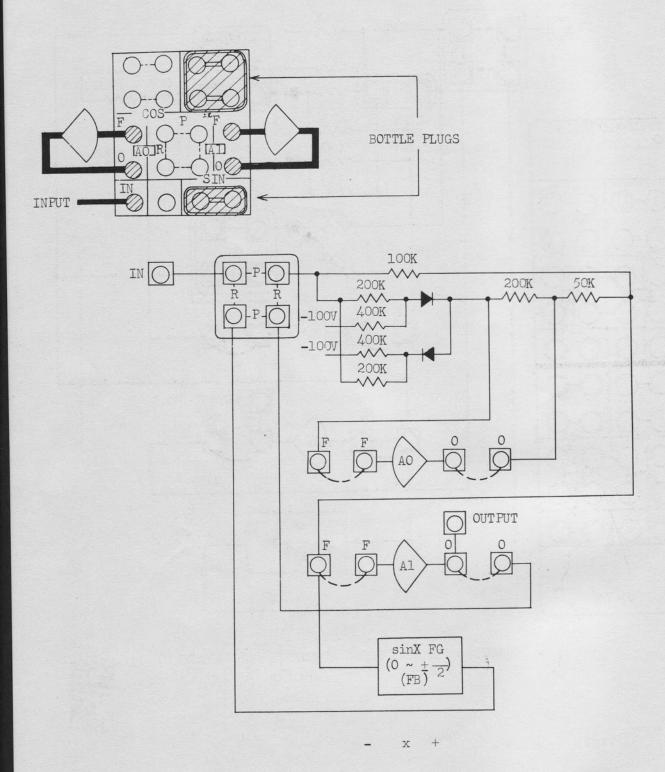

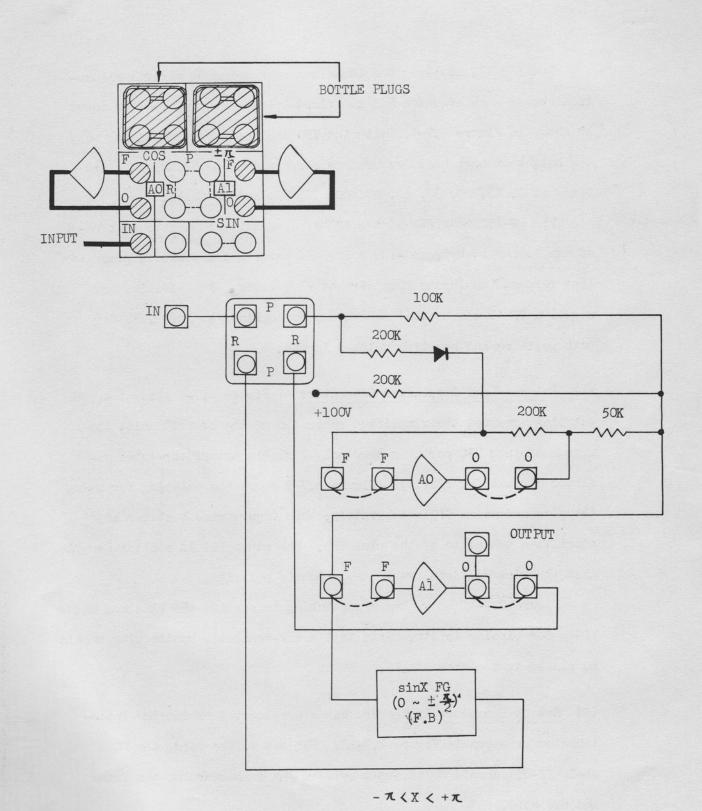

## c. Trigonometric Function Generator FG-153A

The 505 Trigonometric FG contains two individual Trigonometric function generators both of which are terminated at the Pre-Patch Panel. Each generator accepts a voltage of eather polarity. Figure 2.7-4 illustrates simplified schematic and patching block layout. Patching to generate sin X and cos X are given in Figure 2.7-5 and 2.7-6 respectively.

## d. Variable Function Generator FG-151

Frequently in a problem, the dependence of one variable quantity (Y) on another quantity (X) is known only in the form of experimentally obtained data. The Variable Function Generator (VFG) provides a means, with a single component of approximating and generating functions of this type.

NOTE:

- 1.  $R_1$  AND  $R_2$  OHMS IN ALL CASES. 2. CUTPUTS ARE LOG TO BASE 10.

FIGURE 2.7-3 LOG X FG PATCHING AND SIMPLIFIED SCHEMATIC

NOTE: THE SIMPLIFIED SCHEMATIC CORRESPONDS HALF OF THE PATCHING FG-153

FIGURE 2.7-4 TRIGONOMETRIC FG, SIMPLIFIED SCHEMATIC AND PATCHING BLOCK LAYOUT

FIGURE 2.7-5 sinX PATCHING AND SIMPLIFIED SCHEMATIC

FIGURE 2.7-6 COSX PATCHING AND SIMPLIFIED SCHEMATIC

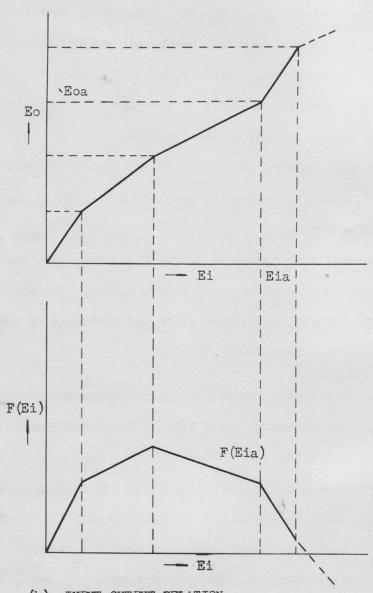

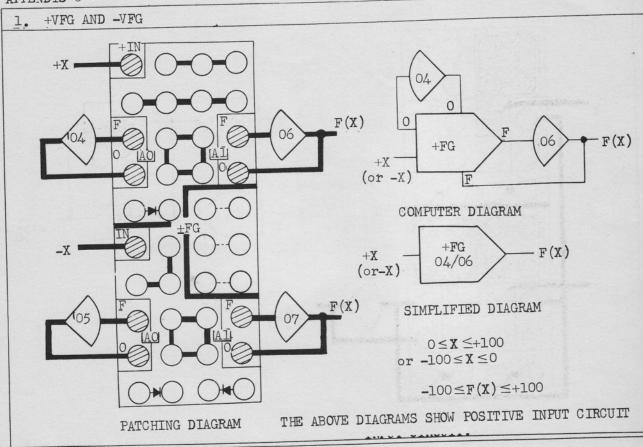

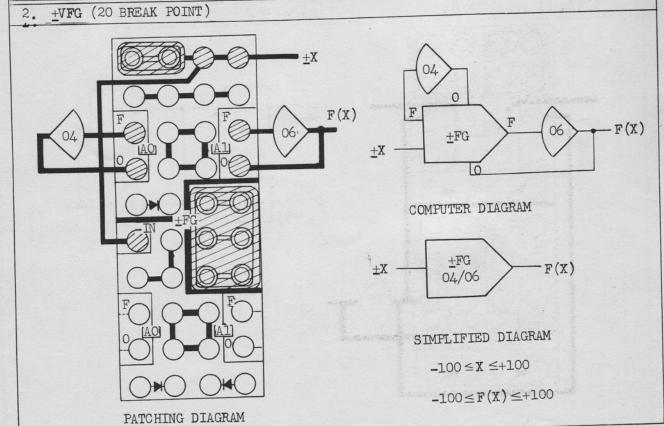

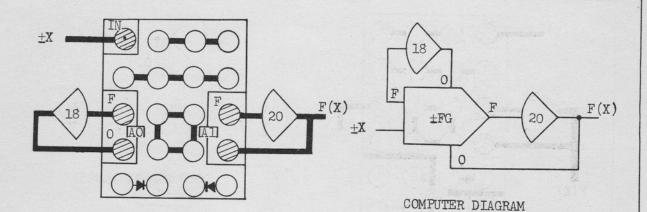

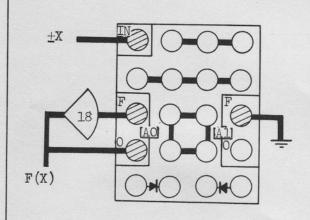

The 505 VFG utilizes the technique of summing of several saturation curves each of which has two fixed breakpoints referred to input as shown in Figure 2.7-7. With the VFG the operator can control only the height of each basic saturation curve since the breakpoints are fixed at 0, 10, 20, 30, 40, 50, 60, 70, 80, and 90 volts.

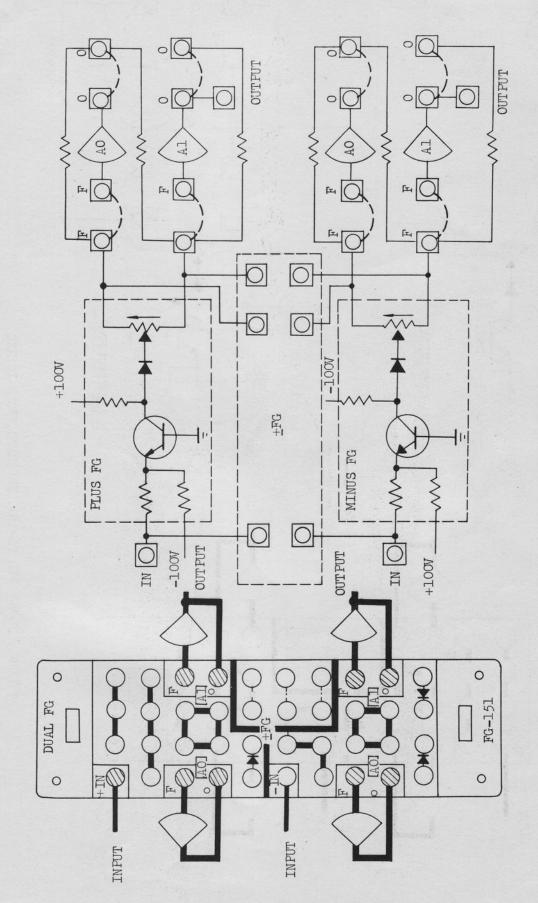

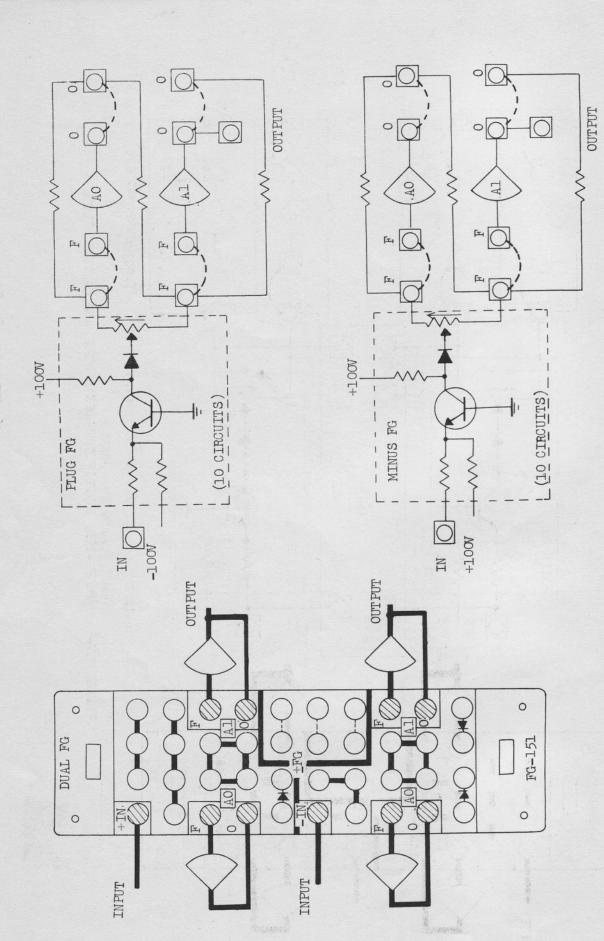

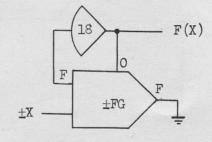

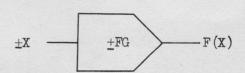

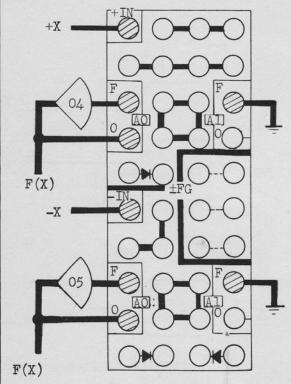

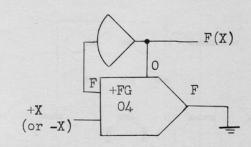

The FG-151 consists of two VFG's: a negative generator that responds to inputs between -100 volts and zero, and a positive generator that responds to inputs from zero to +100 volts. The positive and negative VFG's can be used separately or combined to form ±VFG for both positive and negative voltage inputs.

(1) Patching and Simplified Schematics Figure 2.7-8 shows the VFG patching area and the simplified schematic of the overall unit; the plus and minus VFG portions show only a single transistor-gated resistor circuit for clarity. Figure 2.7-9 shows the patching for using the plus and minus VFG's separately; this figure also contains a simplified schematic of the plus VFG. The minus VFG is similar except that the bias voltages are in the opposite polarity.

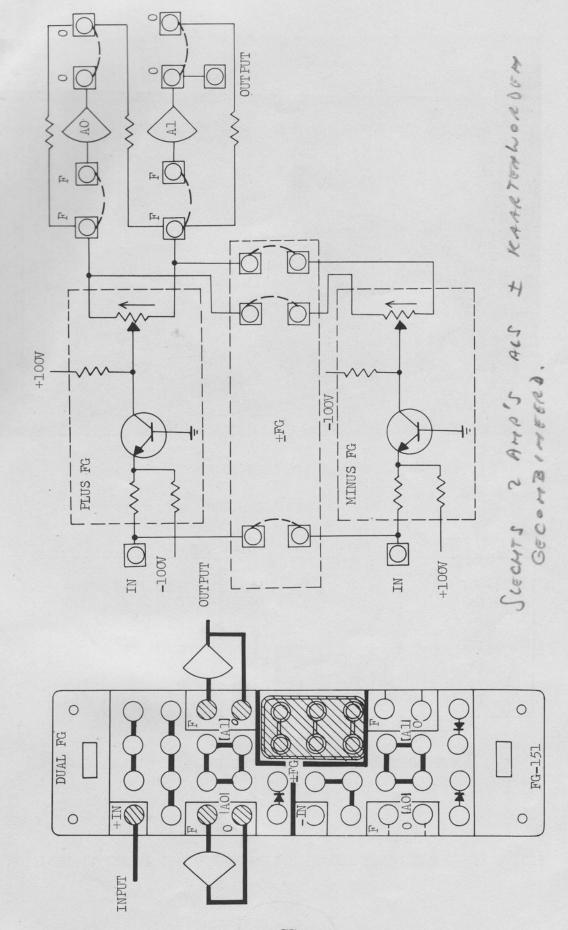

Figure 2.7-10 shows the VFG patching to combine the plus and minus VFG's for bipolar inputs. Note that a six-connector bottle plug should be placed in the area of  $\pm$ FG.

(2) Set Up Procedure The VFG cards are located behind the Potentiometer as shown in Figure 2.7-11. For set up the card, the FG shelf FJ-051 should be inserted between the connectors on the frame and the card.

Each VFG unit has eleven adjustments; They are all F(X) potentiometers to adjust the output of curve height between unitary, incremental inputs of X.

When used in the  $\pm VFG$  combined mode the first pots of the -VFG and +VFG are interdependent.

The first potentiometer permits the operator to set the value of F(X) (at X=0) within the range of +100 to -100 volts. The remaining F(X) potentiometers (10 to 100) permit the operator to set the change of the height to each preceding segment by a voltage of zero to  $\pm 100$  volts.

Figure 2.7-12 is a sample output curve of a +VFG.

This curve is used as the basis for the typical VFG set-up procedure.

The following procedure is for the set-up of a +VFG patched as shown on Figure 2.7-12. The set-up adjustments of the +VFG must be started at X=0 and continued in sequence to X=+100. The procedure for -VFG is accomplished in a similar manner, but starting at X=-100 and in sequence to X=0.

When setting up a VFG for combined plus and minus inputs the operator must start at X=-100, don't make the set-up of X=0 in plus VFG.

FIGURE 2.7-7 PRINCIPLE OF VFG

FIGURE 2.7-8 VFG FG-151, SIMPLIFIED BLOCK DIAGRAM AND PATCHING BLOCK

FIGURE 2.7-9 VFG FG-151, SEPARATE VFG PATCHING

a. VFG CARD LOCATION

| PRE-PATCH PANEL AREAS |                       | VFG LOCATIONS |            |             |             |             |             |             |             |

|-----------------------|-----------------------|---------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|

|                       |                       |               | FG03       | FGO-1       | FG0-2       | FG1-1       | FG1-2       | FG2-1       | FG2-2       |

|                       | OVER-<br>LOAD<br>AMPL | DITH-<br>ER   |            | FG-<br>051A | FG-<br>051B | FG-<br>051A | FG-<br>051B | FG-<br>051A | FG-<br>051B |

|                       |                       |               |            | OR          | OR          | OR          | OR          | OR          | OR          |

|                       | 0I-<br>051            | TW-<br>051    | FG-<br>057 | FG-<br>052  | FG-<br>052  | FG-<br>052  | FG-<br>052  | FG-<br>052  | FG-<br>052  |

b. VFG LOCATIONS AND ASSOCIATED PRE-PATCH PANEL AREAS

FIGURE 2.7-11 VFG CARD LOCATION SHOWING CHASSIS IN SET UP POSITION

## (3) Typical VFG Set-Up Procedure

- (a) Insert the FG shelf between the connectors on the frame and the card.

- (b) Select the F(X) amplifier output (designated Al on Figure 2.9-9) for readout on the DVM (or multi-range voltmeter if the DVM is not available).

- (c) Turn the "SET-OPE" switch on the card to "SET" side, and turn all "SET-RESET" switches to "RESET" side.

- (d) Turn the "SET-RESET" switch of FO to "SET" side and adjust the FO potentiometer by matching the output to the value of F(0).

- (e) Turn the "SET-RESET" switch of Fl to "SET" side and adjust the Fl potentiometer by matching the output to the value of F(1).

- (f) Proceed in sequence the above adjustment to the greater number of F, for the proper DVM readout as listed in the table.

- (g) For optimum accuracy repeat the set-up procedure, starting with step (c).

- (h) Turn the "SET-OPE" switch on the card to "OPE" side.

# e. Variable Function Generator FG-152

The VFG FG-152 is the same to the VFG FG-151 except the break-points. The breakpoints of the FG-152 are -100, -80, -60, -40, -20, 0, 20, 40, 60, 80 and 100 volts. Therefore, the FG-152 covers by itself the whole input range.

FIGURE 2.7-12 SAMPLE VFG OUTPUT CURVE

- 80 -

The function card of the FG-152 is called FG-052, and two FG-052 cards are terminated on the FG-152 patching area.

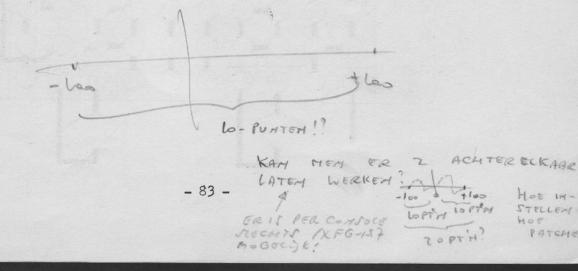

## f. Variable Function Generator FG-157

The Variable Function Generator FG-157 is a versatile device which makes it possible to set up the both coordinates Xn and F(Xn) of each set point n independently. Therefore, with the FG-157, the operator can control both the breakpoint and the height of a given function quite easily. Moreover, each adjustment can be done independently even in same kind of coordinate, so it is very easy to change a portion of the set-up function.

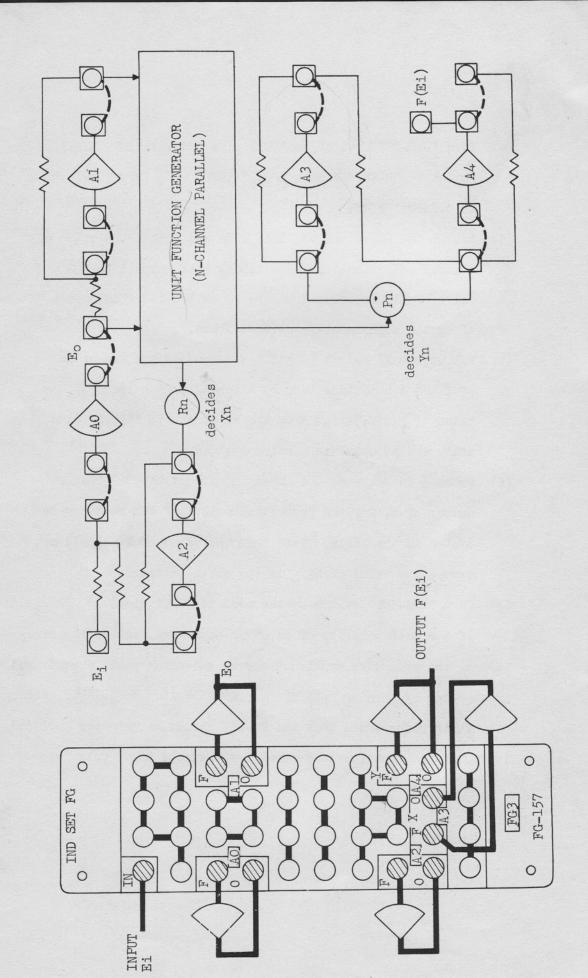

The principle of the FG-157 is explained on Figure 2.7-13. Figure 2.7-14 illustrates the patching for ordinary use of the Function generator.

The following procedure is for the set-up of a FG-157 for positive input patched as shown on Figure 2.7-12. The set-up adjustments of the FG-157 must be started at FO and continued in sequence to F10 on the function card FG-057.

## Typical VFG FG-157 Set-Up Procedure

- (a) Insert the FG shelf between the connectors on the frame and the card.

- (b) Select the X and Y amplifiers for readout on the multirange voltmeter and DVM respectively (if the DVM is not available, both amplifiers should be connected to the multi-range voltmeter alternatively by using the selector system or the function switch.

(a) SIMPLIFIED BLOCK DIAGRAM

(b) INPUT-OUTPUT RELATION

FIGURE 2.7-13 PRINCIPLE OF VFG FG-157

- (c) Turn "OPE-SET" switch to "SET" side and all "SET-RESET" switch to "RESET" side. Keep "+INPUT ± INPUT" switch to "+INPUT" side.

- (d) Put up the FO switch to "SET" side and adjust the value of Y and X potentiometers by matching both outputs to the valve of Y1, Xo. Put down the FO switch to "RESET" side after the adjustments mentioned above.

- (e) Put up the Fl switch to "SET" side and adjust the value of Y and X potentiometers by matching both outputs to one value of Y1, X1. Put down the Fl switch to "RESET" side after the adjustments mentioned above.

- (f) Proceed in sequence the above adjustment to the greater number of F, for the proper voltmeter and DVM readings as listed in the table. Note that the value of Xn should not exceed the value of  $X_{n+1}$  in the above settings.

- (g) Turn "OPE-SET" switch on the cord to "OPE" side.

If the both polarity of input is necessary, set up the function by the procedure mentioned above, and after that, expand the input range by turning "+INPUT — ±INPUT" switch to "+INPUT" side.

It is recommended that the FG-057 should be used for positive input, if the function is defined for a single input polarity.

FIGURE 2,7-14 FG 157, SIMPLIFIED BLOCK DIAGRAM AND PATCHING BLOCK

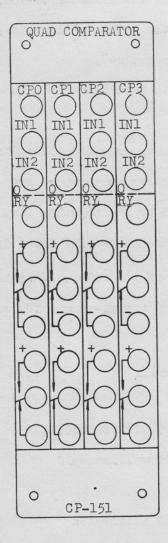

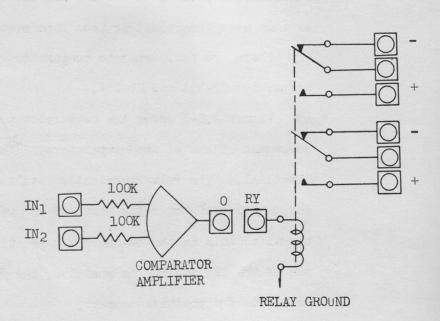

## 8. COMPARATORS CP-151, CP-152

The signal comparator is an automatic switching device that consists of a comparator amplifier and a double-pole, double-throw relay. The amplifier compares two input voltages and energizes or de-energizes the relay, depending on whether the sum of the input voltages is greater than zero (positive) or less than zero (negative).

There are four separate comparator units terminated at a Quad Comparator CP-151 and CP-152.

Figure 2.8-1 shows the comparator patching area and a simplified schematic of one of the comparators. (The other comparators are identical.) The relay termination indicated by the negative sign is the position of the relay when the sum of the IN1 and IN2 input is negative, this is the de-energized position of the relay. When the sum of the IN1 and IN2 is positive, the relay energizes and the wiper swings to the positive contact.

## (1) Comparator Switching Data of CP-151

Relay Switching Time

Typical ..... 5 milliseconds

Maximum allowable ......10 milliseconds

Sensitivity

Typical ..... 30 millivolts

Minimum ..... 50 millivolts

## (2) Comparator Switching Data of CP-152

Relay Switching Time

Typical ......300 microseconds

Maximum allowable ..... 500 microseconds

NOTE: COMPARATOR RELAY SHOWN DE-ENERGIZED

Sensitivity

Typical ..... 30 millivolts

Minimum ..... 50 millivolts

Each model of the comparator has the voltage output which has switching time less than 10 microseconds. The output can drive the integrator mode and etc., directly.

- (3) Set Up Procedure The problem variable that is to control the comparator switching should always be applied to the IN1 termination and the reference or bias voltage should be applied to the IN2 termination. The following is the set-up procedure for the comparator.

- (a) Apply an input to the IN1 termination equal in magnitude and potarity to the desired switching level.

- (b) Connect the wiper of a potentiometer to the IN2 termination; apply reference, opposite in polarity to the IN1 input, to the potentiometer high end.

- (c) Adjust the input to IN2 so the comparator relay is actuated as required when IN1 reaches the switching level. (The output of each comparator can be selected to the selector system.)

- (d) The comparator is now set for use in the problem and should be patched to the appropriate signal sources.

The steps mentioned above can be replaced by the adjusting of the bias potentiometer in the reset mode using the potentiometer selector system, if high accuracy is not required.

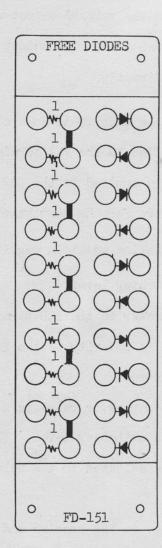

FIGURE 2.9-1 FREE DIODES PATCHING BLOCK AND SCHEMATIC

### 9. FREE DIODES FD-151

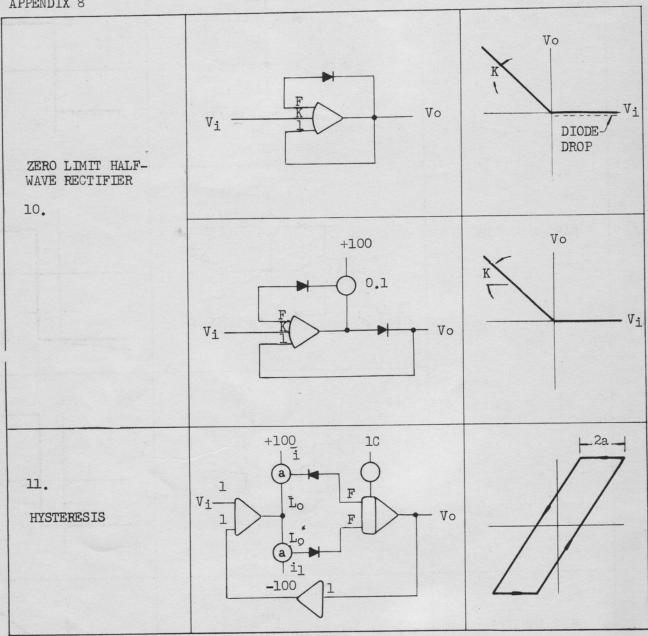

Many non-linear phenomena may be simulated by using the combination of resistors and diodes in the Free Fiodes FD-151 with the potentiometers. Applications will be shown in Appendix 7.

### 10. TRANSFER DELAY ELEMENT TD-151