Section 3

Operation and Control

## CONTENTS

|                      |                                                                                                                 | Page         |

|----------------------|-----------------------------------------------------------------------------------------------------------------|--------------|

| 3.                   | Operation and Control                                                                                           | 3-1          |

| 3.1.                 | Selection                                                                                                       | 3-2          |

| 3.1.1.               | Push-Buttons for Decade Selection of Computing Elements                                                         | 3-2          |

| 3.1.2.               | Address Indication on Digital Voltmeter Display                                                                 | 3-3          |

| 3.1.3.               | Control Push-Buttons for Selection                                                                              | 3-5          |

|                      |                                                                                                                 | 3-7          |

| 3.2.<br>3.2.1.       | Timers Programs of the Digital Control Unit                                                                     | 3-7          |

| 3.2.2.               | Setting of Timers                                                                                               | 3-12         |

| 3.3.<br>3.3.1.       | Control Elements on Digital<br>Control Unit<br>Push-Buttons for Mode Control:                                   | 3-15         |

|                      | "Pause", "Compute", "Hold", "Continue"                                                                          | 3-17         |

| 3.3.2.               | Push-Buttons for Program Selection: "Dauer", "mit Halt", "Repet.",                                              |              |

|                      | "It.aut.", "It.Hand"                                                                                            | 3-20         |

| 3.3.3.<br>3.3.4.     | Program "Single Run" (1 x R) Push-Buttons for Parallel Switching Functions and External Control:                | 3-24         |

|                      | "Eigen", "Fremd"                                                                                                | 3-25         |

| 3.3.5.               | Notes for Push-Buttons "Progr." "Pot.", "Null", "stat.", "dyn."                                                 | 3-26         |

| 3.3.6.               | Push-Button for Overload Stop                                                                                   | 3-26         |

| 3.4.                 | Control Function of the Digital                                                                                 | 2 20         |

| 3.4.1.               | Adapter Unit<br>Push-Buttons of Digital Adapter                                                                 | 3-28         |

|                      | Unit Stop, Run, Lö, HT                                                                                          | 3-29         |

| 3.4.2.               | Clocks and Control Signals of DPF                                                                               | 3-30         |

| 3.4.3.               | Program Control via the DPF                                                                                     | 3-34         |

| 3.4.4.<br>3.4.5.     | Control of Input and Output Devices<br>Control Data Transfer between Digi-<br>tal Adapter Unit and Hybrid Coup- | 3-42         |

|                      | ling Unit                                                                                                       | 3-44         |

| 3.4.6.               | Cross-Connection Lines                                                                                          | 3-47         |

| 3.4.7.               | Alphabetic Listing of Jacks on the DPF                                                                          | 3-48         |

| 3.5.                 | Internal Output Devices                                                                                         | 3-51         |

| 3.5.1.               | Digital Voltmeter                                                                                               | 3-51         |

| 3.5.1.1.             | General                                                                                                         | 3-51         |

| 3.5.1.2.             | Measuring Sequence                                                                                              | 3-52         |

| 3.5.1.3.             | Calibration                                                                                                     | 3-53         |

| 3.5.1.4.<br>3.5.2.   | Printer Control Dual-Beam Storage Oscilloscope                                                                  | 3-53         |

|                      | HPO 771                                                                                                         | 3-56         |

| 3.5.2.1.<br>3.5.2.2. | General<br>Operation                                                                                            | 3-56<br>3-57 |

| 3.6.                 | Balancing and Testing                                                                                           | 3-58         |

| 3.6.1.               | Zero-Instrument                                                                                                 | 3-58         |

| 3.6.2.     | Balancing of the Time Sweep<br>Generator                      | 3-59 |

|------------|---------------------------------------------------------------|------|

| 3.6.3.     | Zero-Balancing of the Opera-<br>tional Amplifiers Push-Button |      |

|            | "Zero"                                                        | 3-59 |

| 3.6.3.1.   | Operational Amplifiers with                                   |      |

|            | Addresses 0 to 5                                              | 3-59 |

| 3.6.3.2.   | Op.Amps.of Adapter Units                                      | 3-60 |

| 3.6.3.2.1. | Drawer Function Generator VFG 801                             | 3-60 |

| 3.6.3.2.2. | Drawer Non-Linear Networks NNT                                |      |

|            | 801 1)                                                        | 3-60 |

| 3.6.3.2.3. | Drawer Electronic Resolver ERS 702                            | 3-61 |

| 3.6.3.2.4. | Drawer Non-Linear Networks NNT                                |      |

| 3.0.3.2.4. | 771                                                           | 3-61 |

| 3.6.3.3.   | Drift-Compensated Operational                                 |      |

| 3.0.3.3.   | Amplifiers                                                    | 3-62 |

| 3.6.3.3.1. | Amplifiers Allocated to the NN-                               | 0 02 |

| 3.0.3.3.1. |                                                               | 3-62 |

|            | Computer Magazine                                             | 3-62 |

| 3.6.3.3.2. | C-Inverterw                                                   | 3-02 |

| 3.6.3.3.3. | Inverters in the Noise Generators-<br>Amplifier Magazine      | 3-63 |

| 3.6.4.     | Static Program Check, Push-                                   |      |

|            | Button "stat."                                                | 3-63 |

| 3.6.5.     | Dynamic Check, Push-Button                                    |      |

|            | "dyn."                                                        | 3-64 |

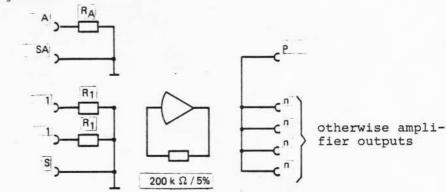

| 3.6.6.     | Principle Circuits of "Check                                  |      |

|            | Modes"                                                        | 3-65 |

| 3.6.6.1.   | Potentiometer Setting, Push-                                  |      |

|            | Button "Pot." depressed                                       | 3-65 |

| 3.6.6.2.   | Static Porgram Check, Push-                                   |      |

| 3.0.0.2.   | Button "stat." depressed                                      | 3-65 |

| 3.6.6.3.   | Zero-Balancing of Operational                                 |      |

| 3.0.0.3.   | Amplifiers, Push-Button "Zero"                                |      |

|            | depressed                                                     | 3-66 |

| 3.6.6.4.   | Dynamic Check, Push-Button                                    | 5 00 |

| 3.0.0.4.   | "dyn." depressed                                              | 3-67 |

| 2 6 7      | Dynamic Zeroing of the Inte-                                  | 5 01 |

| 3.6.7.     |                                                               | 3-68 |

| 2 6 0      | grators Testing of Supply Voltages                            | 3-68 |

| 3.6.8.     | Testing of Supply Voltages                                    | 3-00 |

# LIST OF FIGURES

|                    |                                                                                                                                       | Page |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.2.1/1<br>3.2.1/2 | Program start and program run<br>Time diagram of active control<br>lines of DBG 771 and of digital<br>adapter unit DZ 772 for program | 3-8  |

|                    | "It.aut."                                                                                                                             | 3-11 |

| 3.2.2.             | Clock generation and timer                                                                                                            |      |

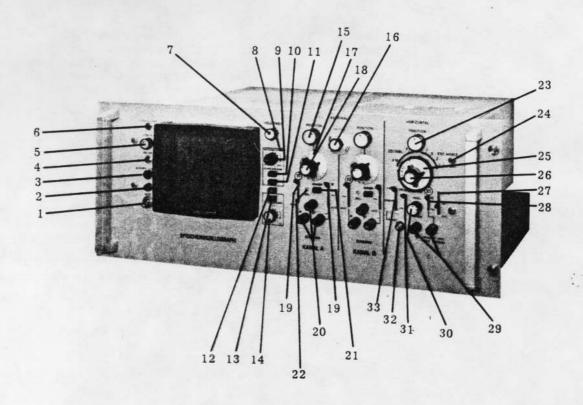

| 3.3.               | control Functions of the control panel of the digital control unit                                                                    | 3-13 |

|                    | DBG 771                                                                                                                               | 3-16 |

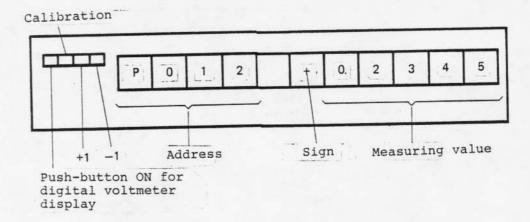

| 3.5.1/1            | Digital voltmeter display                                                                                                             | 3-51 |

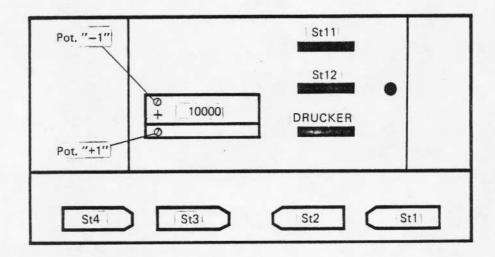

| 3.5.1/2            | Rear side of the digital volt-                                                                                                        |      |

|                    | meter electronics                                                                                                                     | 3-51 |

| 3.5.2.             | Front view of HPO 771                                                                                                                 | 3-54 |

| LIST OF T          | ABLES                                                                                                                                 |      |

| 3.1.2.             | Address indication on digital                                                                                                         |      |

| 2 5 4              | voltmeter display                                                                                                                     | 3-4  |

| 3.5.1.             | Measuring sequence of digital voltmeter                                                                                               | 3-52 |

| 3.6.8.             | Supply voltages                                                                                                                       | 3-68 |

|                    |                                                                                                                                       |      |

#### LIST OF ABBREVIATIONS

Initial Value A Analog Patch Panel APF Operating Unit (Control Unit of Slave Computer) BDZ Print Instruction DB Digital Control Panel (Control Unit of Master Computer) DBG DE Printer ON Digital Patch Panel DPF DVM Digital Voltmeter DZ 772 Digital Adapter Electronic Resolver ERS 702 Sequences (Operating Condition of a Store) Ink-pen Start (XY-Plotter) FA Flipflop FF Basic Clock GT Hold, Hold Instruction H Hold-Phase End HE Manual Clock HT Duty Cycle IPV K Comperator Paper-Tape Control Unit LSZ Erase Lö, lö Space Line LZ Machine Unit (= 10 V) ME Monoflop MF

Non-Linear Networks

NN

| NNT 801 | Drawer, Non-Linear Networks |

|---------|-----------------------------|

| NNT 701 | Drawer, Non-Linear Networks |

| Os      | Oscilloscope                |

| OD      | Oscilloscope Blanking       |

| ОН      | Oscilloscope Unblanking     |

| R       | Computing                   |

| RE      | Computing Phase End         |

| Sch     | Plotter                     |

| SR      | Shift Register              |

| SR2     | Shift Register              |

| St      | Connector                   |

| Ü       | Over-amplify                |

| ÜН      | Over-amplify Hold           |

| VA      | Amplifier Selection         |

| VFG     | Variable Function Generator |

| WT      | Selection Clock             |

| WTR     | Continue                    |

| Z       | Sweep Generator             |

| Z       | Counter                     |

| ZL      | Counter                     |

| ZL 2    | Counter                     |

Timer

Time Constant Control (10 times faster)

ZG

ZS

# LIST OF IMPORTANT DESIGNATIONS AND SYMBOLS

Integrator capacitor  $C_1 = 5000$ , 500, 50, 5 nF

$$K_0 = \frac{1}{C_1 \times R_1}$$

Integration factor  $k_0 = 1$ , 10, 100, 1000 1/s

1 X K1

Machine unit 1ME = 10 V

mn

Address, m digit of tenth, n digit of units

F

Factor of pause phase  $T_p = F_p \times GT$

$F_R$

Factor of computing phase  $\mathbf{T}_{\mathbf{R}}\text{= }\mathbf{F}_{\mathbf{R}}$  x GT

$F_{H}$

Factor of hold phase  $F_{H} = 1$

GT

Period of basic clock

$T_p$

Period of pause phase

$T_R$

Period of computing phase

$T_{H}$

Period of hold phase

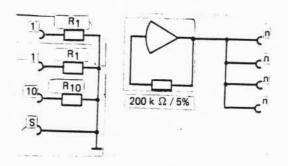

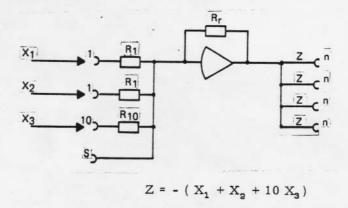

$R_1 = 200 \text{ kOhm}$  $R_{10} = 20 \text{ kOhm}$

Input or feedback resistor

$R_A = 5 \text{ kOhm}$

Resistor within network for initial value

"0", "1"

Binary values

3. Operation and Control

The total operation of the computer is centralized in the digital control unit DBG 771. By means of push-buttons and rotary switches on the front plate, all different functions can be controlled for selection of the computing elements, setting of timers as well as of operation and program modes. Special control circuits are provided for all different operation modes, which need not to be established by patching freely programmable elements, but by depressing a push-button only.

The control possibilities of the computer can be considerably increased when further using a digital adapter unit, permitting a farmost automation of computing and output processes as well as an individual control of integrators and stores.

Except the decoding circuits for the selection position, only digital circuits are used for the control unit. To avoid explanation of technical details within this section (operation and control) the whole functional description is given in the technical manual.

The control unit contains three functional groups:

- 1. Selection

- 2. Time selection

- 3. Control

To each functional group, push-buttons or rotary switches are assigned whose allocation to the respective functional groups is definitely determined by means of a respective designation on the front plate (see annex).

Additionally, the control unit contains:

- two push-buttons for central overload indication and random overload stop

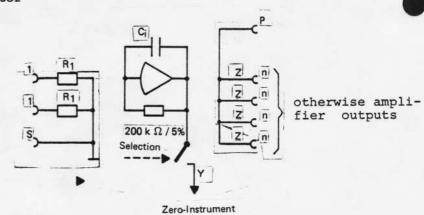

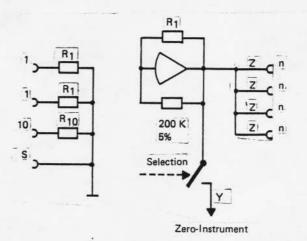

- Zero-instrument for balancing of the operational amplifier by means of two respective push-buttons and balancing potentiometers.

The control unit supplies the respective signals for connected output devices and for a possibly connected digital adapter unit. Further explanations to 1.)-5.) are given in the following.

The functional groups "Selection" and "Control" can be remotely controlled by digital signals with respective coding. In this case, the push-buttons must not be actuated but indicate the arrival and length of the respective signals when illuminated.

Such remote control is possible when using the computer within a hybrid computer system, i.e. when used in combination with a digital computer via a hybrid coupling unit or when connecting a punched-tape control unit LSZ 100.

All push-buttons of the control unit are normally locked in depressed position and simultaneously illuminate. The push-buttons within one push-button row thereby release each other. If, however, the remaining push-buttons within a row should remain in their positions, the respective individual push-button can be released by slightly depressing this push-button or another one of the same row. After activation of a push-button function, the respective push-button illuminates irrespective to a locked position or not (e.g. when used in combination with other push-buttons, automatic run, remote control). They again extinguish, after their function is interrupted by depressing other push-buttons or caused by automatic control.

Any exceptions as to the locking and release of pushbuttons are mentioned in the respective descriptions.

The selection push-button panel is combined within a special panel, designated "selection". The selection also includes the operation of a digital printer. Also connected to the panel is the respective panel for setting the values for servo-set coefficient potentiometers. The selection panel contains all push-buttons for decade selection of the computing elements and six control push-buttons provided in the lower left-hand panel field.

- . The dynamic behavior of the computing element changes

- . during selection because of the connection of the

- . measuring line.

The selection panel contains one push-button row with six push-buttons, designated P and V, as well as two rows with ten push-buttons each, designated 0...9. By depressing a push-button, other push-buttons within the same row are released. For single push-button release, a slight touch must be applied. The whole panel serves for selection of a maximum of 600 computing elements of three computer racks (three analog patch panels) with 200 selectable computing elements each. However, the system must be a combination of a master computer equipped with control unit DBG 771 and one or two slave computers without own control unit. Computers with own control unit DBG 771 being switched in-parallel do not permit a selection from a second control unit, but in this case must be equipped with an adapter control unit BDZ 801 instead of DBG 771.

Of the 200 computing elements that can be selected on each analog patch panel or computer rack, 84 are coefficient potentiometers, 9 are controllable supply voltages, whereas 100 are other elements, such as operational amplifier, multipliers, function generators and special addresses. The remaining positions are not occupied.

3.1. Selection

3.1.1.

Push-Buttons for

Decade Selection of

Computing Elements

The two-decade panel consisting of two push-button rows with ten push-buttons each, designated 0...9 permit entering of 100 address positions between 00 and 99. Coefficient potentiometers and supply voltages thereby are selected via the push-button "P", whereas for amplifiers and other computing elements, push-button "V" is used. Three pairs of push-buttons "P" and "V" are available, designated 0, 1, and 2. The push-button pair designated 0 serves for selection of all elements of the computer in which the control unit is arranged. The push-button pairs 1 and 2 are for selection of elements of the slave computer 1 or 2, which are not equipped with control units.

This means, that an address for selection consists of a letter (P or V) and a two-digit number between 00 and 99. The tens position of the address thereby designates one of the ten fields of the APF, designated 0 to 9, whereas the unit position of the address defines the output of the computing element or a special connection within this field. The unit position always corresponds to the jack designation of the field. Since equal computing elements also have equal unit addresses (exceptions possible only with center fields 2 and 7), the addressing system is easy to learn.

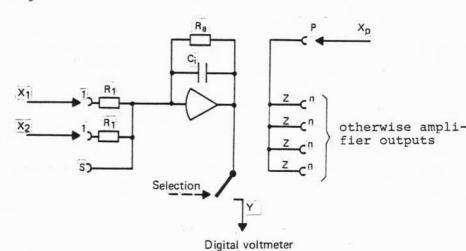

3.1.2. Address Indication on Digital Voltmeter Display Part of the selection is the digital voltmeter display. After entering an address, it appears in the address field of the digital voltmeter. Thereby, a few modifications are possible. E.g. the address is indicated with three digits, containing the leading computer number 0, 1, or 2 according to the computer address (or APF-address) for which the push-buttons "P" or "V" were used.

The computer further contains a real feedback for the selected computing elements, which is based on a letter designation. If, for example, no computing element is available under the selected address (e.g. with partially equipped computers) the indication of a leading letter in the address field of the digital voltmeter does not take place. In all other cases, a letter appears on first position before the three-digit address, according to the following table:

| Depressed             | Code   | Selected                                                                                          | Address                            |                   |

|-----------------------|--------|---------------------------------------------------------------------------------------------------|------------------------------------|-------------------|

| letter<br>push-button | letter | computing<br>element                                                                              | tens<br>position                   | units<br>position |

| P                     | Р      | Coefficient potentiometer                                                                         | 0 - 9<br>(without 2 and 7)<br>2, 7 | 0 - 7.9           |

| P                     | K      | Supply<br>voltages                                                                                | 0 - 8                              | 8                 |

| V                     | I      | Integrator,<br>complementary<br>integrator,<br>store, comp-<br>lementary store,<br>open amplifier | 0 - 9                              | 0,1,2,            |

| ٧                     | S      | Summer, open amplifier                                                                            | 0 - 9                              | 0 - 5             |

| v                     | S      | Inverter of electronic resolver                                                                   | 2,7                                | 7                 |

| V                     | М      | Modulation multiplier                                                                             | 0 - 9<br>(without 2 and 7)         | 7,8               |

| v                     | F      | Variable<br>function<br>generator as<br>inverter                                                  | 0 - 9<br>(without 2<br>and 7)      | 9                 |

| V                     | z      | Selectable<br>jacks on<br>APF                                                                     | 0,2,4 5,7,9                        | 6                 |

|                       |        | on DPF                                                                                            | 7                                  | 9                 |

For example, the selection of V (0)11 causes an address feedback I011 or S011, depending on the respective operational amplifier being programmed as integrator or summer.

An exception is given with the servo potentiometers, (units position 0,1,2,5,6,7). In this case, the feedback "P" is not provided by each single potentiometer, but by the respective potentiometer unit comprising 9 or 10 potentiometers each.

3.1.3. Control Push-Buttons for Selection Six push-buttons in the lower left-hand panel field are provided for special tasks in combination with automatic selection or output of output values of selected computing elements via a connected digital printer. The push-buttons are explained in the sequence of the coupled functions:

a) Push-button "Hand" (manual)

This push-button must be actuated prior to all selection of addresses which are to be entered manually.

b) Push-button "Aut." (automatic)

The selection system contains an automatic selection during which a block of succeeding addresses is scanned subsequently. The block length is 100 positions maximum. As start address, any address can be taken. For operation of the autmatic selection system, the following must be observed:

- Depress push-button "Hand" (manual) and subsequently enter the start address between 00 and 99 via the selection panel.

- 2. Depress push-button "Aut." and wait unitl illumination of the push-button lamp after arrival of the first selection clock. After one second, the automatic address scanning is started. It is continued within a 0.5 Hz-clock. On the digital voltmeter display, any two seconds the complete address designations of the computing elements subsequently appear together with the output values being indicated for visual observation. If a digital voltmeter display is also to be print-out, refer to the respective explanations given under push-button "Print-on". If no final block address is pregiven, the automatic system continuously scans the addresses until reaching position 99, then returns to the start address and remains there. This address scanning is also indicated via the subsequently illuminated address push-buttons. The push-button "Aut." again extinguishes after termination of the scanning, and the lamp of the push-button "Hand" (manual) again illuminates.

- 3. If after depressing of push-button "Aut." and automatic start any final address with higher number is entered, the automatic system interrupts the selection after reaching this address. See also the notes under point 2.

- 4. Also in case of automatic selection, the respectively selected address is indicated by illumination of the respective push-buttons.

- 5. The automatic selection can be stopped at any time by depressing the push-button "Hand" (manual), causing the selection to go over to the entered address.

- 6. The automatic selection can also be interrupted by depressing the push-button "Stop". In this case, push-button "Aut." remains illuminated. After depressing the "Stop"-push-button, which also illuminates, the digital voltmeter is operated periodically. When again depressing the push-button "Aut.", the automatic selection continues from the stopped position to the entered final address or until 99, with return to the start address or to address 00, if no push-button was depressed. Further notes see point 2.

- c) Push-button "Stop"

See also push-button "Aut." point 6. The "Stop"-push-button cannot be released by depressing the push-button "Hand" (manual) which causes the selection to go over to the respective address being entered.

d) Push-button "Print-on" (printer on)

For print-out of addresses and measuring values being indicated on the digital voltmeter, a digital printer can be connected to the computer. When depressing the push-button "Print-on", a print instruction is supplied to the digital voltmeter together with a certain measuring instruction, which become effective. At the following time points:

1. During operation of the automatic selection (push-button "Aut."depressed). Each automatically scanned address is print-out by indicating the complete address feedback and value. The scanning clock thereby increases from 0.5 Hz to 2 Hz, so that scanning, indication and print-out of an address position takes place within a 0.5 speriod. If no address feedback takes place, i.e. element not available within the system, the position will not be print-out. The manually entered start address also is not print-out at the start, but after termination of the scanning sequence, after repeated return to the start address. E.g. in case of 100 positions, print-out of start address 00 takes place after reaching position 99.

When entering a final address, no return to the start address will take place, and thus also a print-out will not occur. A desired print-out must then be initiated by shifting the start address by one position. Print-out of start address 00 with subsequent entering of a final address is not possible during automatic mode, and must be individually carried out by depressing the push-button Print-instr. or via the digital adapter unit.

2. During program modes "Repetitive computing" and "Automatic iterating computing". Print-out takes place at the end of the preset computing time. Print-out of address and address value thereby takes place within the phase Hold, (which must be given for at least 100 ms) following to the phase computing.

3. Automatically after each terminated setting of a servo-set coefficient potentiometer. Setting of the potentiometer value takes place via the setting panel, whereby the setting process is initiated by depressing the respective push-button "POT" located beside.

Then the respective potentiometer address and the value reached by the servo-set potentiometer is indicated on the digital voltmeter and print-out via the printer (not however, the entered potentiometer value).

e) Push-button "Druckbef." (print instruction)

By means of this push-button, print-instructions can be given at any time. In such a case, the respective address being indicated on the digital voltmeter is print-out together with the address value, if the push-button "Print-on" previously was actuated. The push-button "Druckbef." (print-instruction) is not locking and therefore must be again actuated for each print-out. A parallel print-instruction is possible from the digital adapter unit.

f) Push-button "Extern"

After depressing this push-button, all other pushbuttons of the selection panel become ineffective, which also applies for the setting panel of the servo potentiometers.

Simultaneously, a switch-over takes place to external address input by using digital signals, which can be connected via a jack provided on the rear side of the control unit. Input of servo potentiometer setting values is possible via a central setting line (e.g. from a hybrid coupling unit). By depressing the push-buttons "Hand" (manual) or "Aut." (automatic), the effect of the push-button "Extern" can be cancelled. Normally, the push-button "Extern" is used within hybrid computer systems or when using a punched-tape control unit.

3.2. Timers

3.2.1.

Programs of the

Digital Control

Unit

The digital control unit contains fixed-wired programs for control of integrators or stores. A detailed description is given in section 3.3. In the following, a general survey is given.

On the front panel of the digital control unit, there are two vertical push-button rows arranged within a field, designated "Control".

The following programs can be set via the left-hand row:

| Program                        | Push-button |

|--------------------------------|-------------|

| Continuous                     | Dauer       |

| Computation with Hold          | mit Halt    |

| Repetitive computation         | Repet.      |

| Autmatic iterative computation | It.aut.     |

| Manual iterative computation   | It.Hand     |

The following operation modes can be entered via the right-hand push-button row:

| Operation mode | Push-button |

|----------------|-------------|

| Pause          | Pause       |

| Compute        | Rechnen     |

| Hold           | Halt        |

| Continue       | Weiter      |

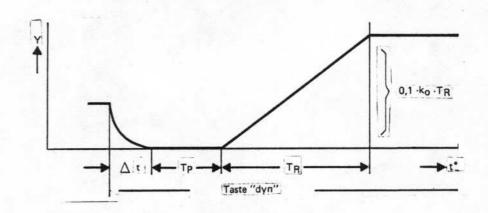

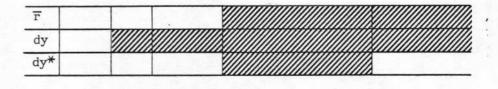

After depressing the push-button "Compute", the selected program is started, beginning with a 1/0-edge of the basic clock. Thereby, a delay time  $\Delta$ t, between 0.5 and 2 seconds (see Fig. 3.2.1/1) is given due to relay switching times.

Fig. 3.2.1/1 Program start and program end

A program is characterized by a certain phase sequence. One distinguishes between:

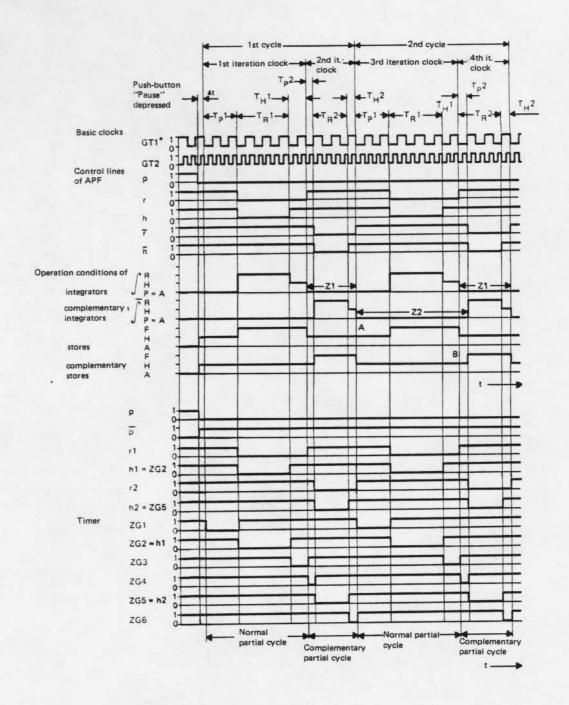

a) Phase Pause 1, phase endurance T<sub>p</sub>1 Phase Compute 1, phase endurance  $T_R^1$  with normal integrators Phase Hold 1, phase endurance T<sub>H</sub>1

b) Phase Pause 2, phase endurance Tp2 Phase Compute 2, phase endurance  $T_R^2$  with complementary integrators Phase Hold 2, phase endurance  $T_{\rm H}^{\,2}$

For the programs "Continuous", "with Hold", "Repet." only the phases of group a) are of importance, thereby index 1 can be omitted. During a phase, the control signals of the active control lines (e.g. r, h, r, h, ZG1) have a constant value of binary 1 or binary 0.

The phase endurance is set on the digital control unit in the respective field designated with "time selection". The upper field half thereby is used for the phases of group a), with phase endurance  $T_p1$ ,  $T_n1$ ,  $T_n1$  or  $T_p$ ,  $T_p$ . The lower field half is provided for the phases of group b) with the phase endurance  $T_p2$ ,  $T_p2$ , T<sub>H</sub>2, respectively.

In the following, the programs of the digital control unit are outlined:

- 1) Program "Continuous computation" The program starts with the Pause-phase, followed by a computing phase, which is unlimitted by the program and thus is not depending on the setting of the timers.

- 2) Program "Compute with Hold" Program run: Phase Pause, phase Compute, phase Hold. The Hold-phase is independent from the timer setting. It can be terminated by depressing the push-button "Continue". Then, phase Compute and phase Hold are following.

- 3) Program "Repetitive computation" The program consists of a sequence of same cycles. Each cycle contains three phases in the following time sequence: Pause, Compute, Hold.

- 4) Programs "Automatic iterative computation" and "Manual interative computation". These programs consist of an alternative sequence of two cycles which are controlled by a normal and complementary computing circuit.

## a) Normal computing circuit

| normal partial cycle | Pause phase | normal partial cycle | Pause phase<br>Z 1 |

|----------------------|-------------|----------------------|--------------------|

|----------------------|-------------|----------------------|--------------------|

### b) Complementary computing circuit

| Pause phase complementary Paus Z 2 partial cycle Z 2 | se phase complementary partial cycle |

|------------------------------------------------------|--------------------------------------|

|------------------------------------------------------|--------------------------------------|

Machine time t\*

In their timely sequence, the cycles are composed of following phases:

- a) normal partial cycle phase Pause 1, phase Compute 1, phase Hold 1

- b) complementary partial cycle phase Pause 2, phase Compute 2, phase Hold 2

Whereas one computing circuit performs a cycle, the other has a Pause-phase, which is abbreviated Z 1 or Z 2. The normal partial cycle is identical to the cycle of the program "Repetitive computation", since an integrator with certain wiring of its control inputs performs the same computing operations during a cycle of program "Repet." and during a normal partial cycle of program "It.aut."

Due to graphic reasons, GT1/GT2 given in a ration of 1:2. Practically, this ratio can be set only in powers of tens.

Fig. 3.2.1/2 Time diagram of active control lines of DGB 771 and of digital adapter unit DZ 772 for program "It.aut."

3.2.2. Setting of Timers All clocks for computer programs as well as for control of the digital elements in the digital adapter unit are centrally generated in the control unit. All freely selectable clocks thereby can be set by means of ten rotary switches provided on the front plate.

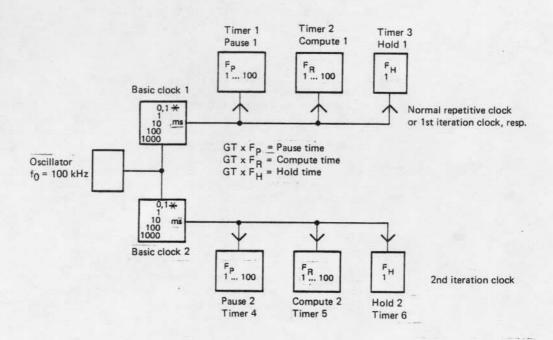

All different clocks are derived from the 100 kHz basic clock of a central crystal oscillator. Two basic clocks GT1 and GT2 are generated by means of a 5-stage frequency divider which permits independent clock setting to 1 kHz, 100 Hz, 10 Hz and 1 Hz. Accordingly, the designation of the two rotary switches for basic clock 1 and 2 are 1 ms, 10 ms, 100 ms and 1 s. Because of the operating condition "10x faster", which for example can be set by depressing the push-button "10x", an additional basic clock of 0.1 ms = 10 kHz is reached in switch position "1ms". Each of the basic clocks thereby influences three digital timers, (see Fig. 3.2.2.). The timers 1,2 or 4,5 can be preset between 1 and 100 by means of two rotary switches, whereas timers 3 and 6 are fixed to 1. The timers are controlled by the preset basic clock in a fixed sequence, by counting reverse from the preset position. After reaching Zero-position, they supply the different signals for control of computing elements via central control lines.

The settable time results from a multiplication of the timer setting by the setting of the respective basic clock. The respective computing condition of the system is indicated via three lamps provided in the upper and lower half of the time selection panel:

Yellow lamp on:

Pause phase 1 or 2 effective or push-button "Pause" depressed

Green lamp on:

Computing phase 1 or 2 effective

Red lamp on:

Hold phase 1 or 2 effective or push-button "Hold" depressed or Hold-control operative.

By depressing the push-button "10x" in the manual potentiometer field, the basic clocks GT1 and GT2 are reduced by the factor 10 (e.g. from 1 ms to 100  $\mu$ s). Thus, the times of all timers are also shortened by factor 10.

Together with time shortening, the integration factors of the integrators are enlarged by factor 10 because of the integrator capacitor switch-over (e.g from  $k_0$  = 1000 s<sup>-1</sup> to  $k_0$  = 1000 s<sup>-1</sup>). This means, that a fast-time scale by factor 10 is reached after depressing the push-button "10x", or a slow-time scale by factor 10, after the depressed push-button "10x" is again released.

<sup>\*</sup> Only during operation mode "10x faster"

Fig. 3.2.2. Clock generation and timer control

The operation mode "10xfaster" can be controlled also by the DPF, see also 3.4.3.

#### Example:

Setting of the Pause-phase endurance

For example, Pause-phase 1 is given as to the operation in the "time selection"-field, whereby the black designation of the field is valid. The settings of both rotary switches for timer 1 result in factor  $\mathbf{F}_p$  (see Fig. 3.2.2) according to the black designation. The factor being within 1 and 100 must be multiplied by the setting of the rotary switch for basic clock 1. The phase endurance is resulting, if the computer is not operated "10xfaster". In this condition, the phase length is smaller by the factor 0.1 than the read value. Setting of phases between 0.1 ms and 100 s with two digits is possible.

The time setting for other phases takes place accordingly, except the phases Hold 1 and Hold 2, which are identical to the times of basic clock 1 and basic clock 2.

| Phase     | Time period            | settable by | means of             |

|-----------|------------------------|-------------|----------------------|

| Pause 1   | Timer 1                |             | two digit            |

| Pause 2   | Timer 4                |             | two digit            |

| Compute 1 | Timer 2<br>Timer 2 and | 1           | two digit four digit |

| Compute 2 | Timer 5                |             | two digit            |

| Hold 1    | Basic clock            | 1           | one digit            |

| Hold 2    | Basic clock            | 2           | one digit            |

The white designation of the time selection panel refers to the four-digit setting of phase Compute 1, whereas the black designation is used for all other phases.

#### Four-digit setting of computing phase length

The four-digit setting is limitted to the program types "Repetitive computation" and "Compute with hold". The rotary switches of timer 1 which otherwise are used for setting of the time period T<sub>1</sub>1 are used also for setting the computing phase. The white designation becomes valid, the rotary switch for basic clock 1 must be set to 10 ms or to 1 ms. With regard to the white designation, the setting of timers 2 and 1 results in factors by sum formation, which are between 1 and 10 000.

This factor must be multiplied by the setting of the rotary switch for basic clock 1. If not set to operation mode "10xfaster", the computing time is resulting. Computing phase lengths between 0.1 ms and 100 s are possible. The Pause-phase length cannot be set, it is determined to 1 s. The time period of the Hold-phase amounts to approx. 1 s.

For four-digit setting of the computing phase period, the time sweep generator (jacks Z on APF) is switched-off.

3.3.

Control Elements

on Digital Control

Unit

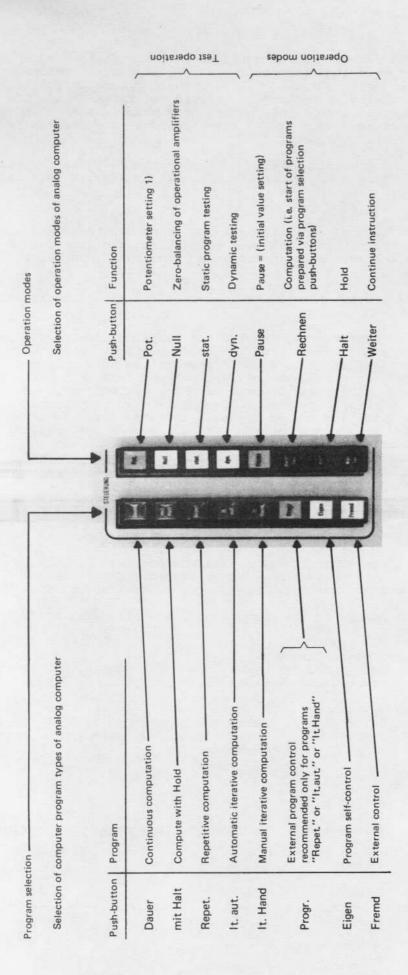

The control panel for setting of operation modes, computing programs and test operations is combined in a push-button panel designated "Steuerung" (control).

The two push-button rows thereby are allocated as follows:

The left-hand push-button row contains all functions for program selection. The push-buttons, however, do not initiate active processes but are used only for respective preparation. The push-buttons of the right-hand push-button row are used for active functions (operation modes) which partially must be prepared by actuating respective push-buttons of the left-hand row. This arrangement provides a better information about the operating conditions of the computer and furthermore enables a more flexible remote control of the modes. The latter is especially important when using the computer within a hybrid computer system, in which a digital computer supplies coded instructions for selection of the computing program and for different settings within the programs to the control unit via direct control lines.

All push-buttons illuminate when depressed, and also if not depressed but if the respective program or operation mode is activated by remote control.

The colors of the push-buttons are allocated as follows:

green push-buttons

left-hand: right-hand: presetting of computing programs, compute start, continue instruction

yellow push-buttons

left-hand: right-hand: external program control

operation modes Pause and potentiometer

setting

red push-buttons

operation mode Hold

white push-buttons

left-hand: right-hand:

setting for self and external control setting for balancing and testing

This push-button permits control preparation of the analog computer for potentiometer setting. The setting process for the servo-set potentiometers is started only after depressing the push-button "POT" on the desired value-input panel.

Fig. 3.3. Functions of the control panel of digital control unit DBG 771

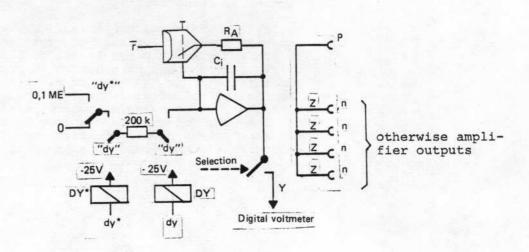

If computing runs within preselected programs are started in one of the two modes for computation (push-buttons "Compute" and "Continue"), the function group "Control" and "Time selection" are combined. The same applies for operation mode "dynamic testing" of the integrators. (Push-button "dyn.").

3.3.1. Prior to Functions for Mode Control: to point-"Pause", "Compute", "Hold", ween the "Continue"

Prior to the following description of the push-button functions of the "Control"panel, it is necessary to point-out to the different functional behavior between the

operation condition of the computer with the different modes "Pause", "Compute", "Hold", according to the depressed mode push-buttons

#### and the

computing run in the computer, which in the compute mode consists of the subsequent following phases "Pause", "Compute", "Hold" or variations thereof.

### Push-button "Pause" (operation mode "Pause")

By depressing the yellow push-button "Pause", all previously started computing runs being either in the phases "Pause", "Compute" or "Hold" (push-buttons "Compute" or "Continue") or in operation mode "Hold" (push-button "Hold" depressed), are terminated and replaced by the "Pause"-mode. All other push-buttons of the same row are released and thus also other operation modes are replaced by "Pause"-mode. In this mode, all integrators and stores carry out the initial condition programmed on the APF (charging of computing or storing capacitors to initial value). In the "Pause"-phase, only the integrators take-over the initial conditions.

During operation mode "Pause", programming is effected on the analog patch panel, whereas program selection takes place on the left-hand push-button row of the control field. When switching-on the computer by means of the push-button "On", the push-button "Pause" also should be depressed.

# Push-button "Compute" (operation mode "Computation"

By depressing the gree push-button "Compute", all computing runs are started whose program previously was prepared by means of the green program selection push-buttons of the left-hand push-button row. When depressing the push-button "Compute", the previously set modes "Pause" or "Hold" are replaced and the respective push-buttons are released.

All computing runs are started after depressing the push-button "Compute" with a Pause-phase  $\mathbf{T}_{\mathrm{p}}$ , whose period was fixed by means of the rotary switch setting in the "time selection"-field (timer 1 and basic clock 1 or timer 4 and basic clock 2). The length of the desired computing phase  $\mathbf{T}_{\mathrm{p}}$  is preset by a respective rotary switch setting of timer 2 and basic clock 1 or timer 5 and basic clock 2, respectively. The "Compute"-mode is terminated by the "Pause"-mode (take-over of new initial conditions for integrators and stores, patched on the APF). This takes place by depressing the push-button "Pause".

The "Compute"-mode is interrupted by different control instructions and replaced by the mode "Hold" (integrators maintain the momentarily given output voltages, as stated in the following section under 1 to 5).

## Push-button "Hold" (operation mode "Hold")

By depressing the red push-button "Hold", all computing runs during the "Compute"-phase are interrupted and go to operating condition "Hold". The integrators and stores thereby maintain the respective momentary output voltage. If during actuation of the "Hold"-push-button, a computing run is in the phases "Pause" or "Hold", these phases will follow. A repeated start of the computing run is then possible only by releasing the push-button "Hold" via the push-button "Compute"-push-button.

The following possibilities are given to interrupt the "Compute"-mode and to replace it by the mode "Hold" or phase "Hold":

- 1. By depressing the push-button "Hold"

- 2. By patching relay ground to the white jack H with green diagonal in field 2 or 7 on the APF.

- 3. By connecting binary "0" to jack II on the digital patch panel of the digital adapter unit.

- 4. By means of an overload of a computing element, if the white push-button "with Hold" located beside the red push-button "U" on the left-hand front panel was actuated, (white push-button illuminates).

- 5. After the preset time  $T_{\rm R}$  of the "Compute"-phase, if the programs "with Hold" or "It.Hand" were entered.

The following possibilities are given to again clear the "Hold"-operation mode:

By depressing the push-button "Compute" precondition is however, that the push-button "Hold" was depressed during the "Compute"-phase. a) Program type "Continuous computing" (push-button "Continuous"). Computation is started from the momentary values.

From this time on, a time sweep voltage is used.

b) Further program types

(push-buttons "with Hold", "Repet.","It.aut.",

"It.Hand"):

Computation starts with the momentarily reached values. According to the setting of GT1 or GT2, up to 2 x basic clock time is loss for the preset computing time T<sub>R</sub>1 or T<sub>R</sub>2. A time sweep voltage is started at the reached values, but because of the missing computing time (which is not considered by the saw tooth generator) does no longer reach value 1 (+ 10 V) at the end of the "Compute"-phase. To prevent this error, a respective computing time setting should be used for the program "with Hold", to replace the depression of push-button "Hold", e.g. for observing intermediate values. A repeated computation start then takes place by means of the push-button "Continue".

- 2. By depressing the push-button "Pause".

- 3. By depressing the push-button "Continue".

Only in combination with the programs "with Hold" or "It.Hand", during which the "Hold"-phase is automatically reached after a preset time T<sub>R</sub>. The computing run is then continued with the phase compute, (based on the momentarily reached values) or with the phase "Pause". If previously the "Hold"-push-button was depressed, the limitation under 1b must be observed (can be avoided by basic clock synchronous holding and starting via the DPF).

- 4. By removing the relay ground on the APF from the white jack H with gree diagonal in fields 2 and 7. Then a computing run interrupted in the "Compute"-phase is continued with phase "Compute" without intermediate "Pause"-phase. Limitations are given as mentioned under 1b (see push-button "Compute", see also 3.).

- 5. By removing the binary "0" from the red jack H on the DPF of the digital adapter unit. Then a computing run interrupted in the "Compute"-phase is continued with phase "Compute" without intermediate "Pause"-pahse. Limitations are given as mentioned under 1 b (see push-button "Compute", see also 3.).

- After "Hold" caused by overload of a computing element.

- a) By depressing the push-button "Pause" and removal of the overload. Repeated start is then possible by depressing the push-button "Compute".

- b) By releasing the large white push-button "with Hold" at the left-hand side of the control unit.

The cancellation of a Hold-lock caused by overload results in a continued "Compute"-phase, started from the momentarily reached values.

Limitations are given as mentioned under 1 b (see push-button "Compute", see also 3.).

#### Push-button "Continue"

By depressing the freen push-button "Continue", a computing run is again automatically started which previously was stopped in operation mode "Hold". The push-button "Continue" is used only in combination with the depressed program selection push-buttons "with Hold", "Continuous" or "It.Hand". The program "It.Hand" (manual) is started with a "Pause"-phase.

Program "with Hold", however, is started with a "Compute"-phase, based on the momentarily reached values. This differs from the normal use of starting a computing run with a "Pause"-phase.

When depressing the push-button "Continue" in combination with the "Continuous"-program, a single sweep voltage (Z-voltage) is caused with time values set by means of timer 2.

The function of the "Continue"-push-button can be controlled in-parallel from the DPF of the digital adapter unit. This requires programming of a 1/0-change at the freen jack WTR.

3.3.2.

Push-Buttons for

Program Selection:

"Dauer" (continuous),

"mit Halt" (with Hold)

"Repet.", "It.aut.",

"It.Hand" (manual)

The green program selection push-buttons of the lefthand row serve for presetting computing programs which can be controlled in different operation modes by means of the push-buttons mentioned under 3.3.1. A short survey of the fixed-wired programs of the digital control unit is given in section 3.2.1. In the following, a few additional details are given.

# Push-button "Continuous" (program "Continuous computation")

The program "Continuous computation" is prepared by depressing the gree push-button "Continuous". The computing time is stopped only by depressing the push-button "Pause". For interrupting the program with succeeding transfer to the "Hold"-mode, the possibilities 1 to 4 are given, as mentioned under 3.3.1. (push-button "Hold"). The different start possibilities are explained in subsections 1, 2 and 4 to 6.

## Push-button "with Hold" (program "Computation with Hold"

The program "Computation with Hold" is prepared by depressing the green push-button "with Hold". The program starts with the "Pause"-phase (phase length  $\mathbf{T}_{\mathrm{p}}$ ). The computing phase can be set either two or four digit; for two-digit setting by means of timer 2 and basic clock 1, for four-digit setting by means of timer 2, timer 1 and basic clock 1 (white designation). After the computing phase  $\mathbf{T}_{\mathrm{R}}$  the operational condition "Hold" is reached. Further computing phases may then be started by depressing the not locking push-button "Continue", whereby further computing phases are always terminated in condition "Hold". The "Pause"-phase  $\mathbf{T}_{\mathrm{p}}$  thereby will be omitted, so that between the subsequent computing phases no initial value conditions are taken over by integrators and stores. The length of the subsequent computing phases can be changed by adjusting the "Pause"-phases  $\mathbf{T}_{\mathrm{R}}$  after reaching operation mode "Hold".

The computing run is terminated only by depressing the push-button "Pause".

For interruption before reaching the preset computing time with subsequent transfer to operation mode "Hold", the same possibilities 1 to 5 are given, as mentioned under 3.3.1. (push-button "Hold"). The different start possibilities also correspond to those mentioned under points 1 to 6.

The function of the push-button "Continue" can be controlled in-parallel from the DPF of the digital adapter unit. Therefore, programming of a 1/0-change at the green jack WTR is required.

#### Push-button "Repet." (program "Repetitive computing)

The program "Repetitive computing" is initiated by depressing the green push-button "Repet." and again terminated by push-button "Pause". For interruption of the computing run by means of the push-button "Hold", see also respective notes given in section 3.3.1, points 1 to 4. As to a repeated start, points 1, 2 and 4 to 6 are valid.

When setting the Pause time  $T_p$ , it must be observed that its value is  $1/k_0$  of the smallest integration factor  $k_0$  of the integrators patched on the APF. (E.g. 1 s at  $k_0$  = 1 s-1). Otherwise, computing errors could occur because of incomplete charging of the integrator capacitor to the voltage value of the initial conditions.

# Push-button "It.Aut." (program "Automatic interative computation")

The program "Automatic interative computation" is prepared by depressing the green push-button "It.aut.".

The program is used for automatic iterative computing with two groups of integrators or stores. These two groups are formed by programming integrators and stores as normal or complementary computing elements on the APF. The program run can be seen in Fig. 3.2.1/2. A four-digit setting of the computing phase is not possible.

The basic clocks 1 and 2 and the timer settings can be selected different for each of the two alternating interation clocks. Thereby, it must be observed that the sum for the phases "Pause", "Compute" and "Hold" of the iteration clock plus the smaller basic clock time must be equal to the basic clock time of the second iteration clock or an even multiple of it. Otherwise, no defined clock transfer is ensured.

The following equation must be given:

$(F_n + F^R + 1) \times GT_K = n \times GT_1 \quad (n \ge 1, even)$  with

GT<sub>k</sub> = set shorter basic clock

GT; = set longer basic clock

F, = setting of Pause time factor with

shorter basic clock time

FR = setting of computing time factor with shorter basic clock time

With same basic clock setting for both iteration clocks, the equation is always given so that no further attention must be paid.

The program is terminated by depressing the push-button "Pause". For interrupting the com

For interrupting the computing run by means of the pushbutton "Hold", see respective section 3.3.1., points 1 to 4, or points 1, 2 and 4 to 6 for repeated start, respectively.

It must always be observed that the resulting Pause time prior to the "Compute"-phase must be at least  $1/k_0$  of the smallest integration factor  $k_0$  of the integrators patched on the APF. (E.g. 1 s at  $k_0 = 1$  s<sup>-1</sup>). The resulting Pause-phase for an interation clock is composed of the length of the second iteration clock plus the set Pause-time  $T_p$ . This condition can always be met by prolongation of  $^pT_p$ . If not, computing errors may occur because of an incomplete charging of the integrator capacitor to the voltage value of the initial conditions.

Push-button "It.Hand" (It.manual) (program iterative computation with manual start)

This program is prepared by depressing the green pushbutton "It.Hand" (It.manual). It farmost corresponds to the automatic iterative computation, with the following differences:

After termination of the first iteration clock with the phases "Pause 1", "Compute 1" and "Hold 1", all normal integrators remain in phase "Hold". The normal stores remain in condition "Follow". The illumination of the red lamp for the first iteration clock, located in the upper part of the "Time selection "-field, indicates that the "Hold"-phase is reached. This phase remains until actuating the push-button "Continue". Then, the phase "Hold" for the first iteration clock goes over into a Pause condition "Pause Z1". (Red lamp extinguishes, yellow lamp illuminates). Now, the normal integrators patched on the APF will take-over the initial conditions, whereas the normal stores keep their output values given at the switching time point.

Simultaneously, the second iteration clock is started, running through the phases "Pause 2", "Compute 2", "Hold 2" until finally stopped in phase "Hold 2" (red lamp of lower part of "Time selection"-field illuminates). Now the complementary integrators keep their values, and the complementary stores follow-up, whereas the normal integrators are still in the Pause-condition, and the normal stores keep their values.

A repeated actuation of the push-button "Continue" then causes the complementary integrators to go over into Pause-condition "Pause Z2", and the complementary stores to go over from "Follow" to "Hold", whereas the normal integrators run through the phases "Pause 1", "Compute 1", "Hold 1" being followed by the normal stores.

Each actuation of the "Continue"-push-button thus causes an iteration clock which is started with the settable time  $T_p$  of the "Pause"-phase. As to the setting of Pause-phases, Compute-phases and Hold-phases, see also respective chapter push-button "It.aut.".

There are no conditions for the selection of the basic clocks. A four-digit setting of the compute-phase  $T_R^{\,\,1}$  is not possible.

The program is terminated by depressing the push-button "Pause". For interruption of the computing run by means of the push-button "Hold", see respective notes given under 3.3.1. points 1 to 5, as well as points 1 to 6 for a repeated start.

A change of the iteration clocks can be controlled not only by means of the push-button "Continue", but also from the DPF of the digital adapter unit. There, the blue jacks H1E, H2E, 1T2 and 2T1 are used. Further details see section 3.4.3.

It must be observed that the resulting pause time prior to the start of the "Compute" phase must be at least  $1/k_0$  of the smallest integration factor  $k_0$  of the integrators patched on the APF (e.g. 1 s at  $k_0 = 1$  s  $^{-1}$ ). The resulting pause phase for an iteration clock is composed of the length of the respective second iteration clock, of the time period until generation of a "Continue"-instruction and of the settable pause time  $T_p$ . With manual actuation of the "Continue"-push-button, this condition practically is always met, but must be considered in case of control for the digital adapter unit.

The condition can always be met by a respective prolongation of  $T_{\rm p}$ . If not, computing errors may occur by incomplete charging of the integrator capacitors to the voltage value of the initial condition.

3.3.3. Program "Single Run" (1 x R) By depressing the push-buttons "Fremd" (external) and "Progr." (program), the "Single Run"-program is called. Further push-buttons of the control panel may be depressed, but do not influence the program run. After program call, the push-buttons "Progr.", "Eigen" (self) "Fremd" (external) and "Halt" (hold) will illuminate.

The program can be started:

from the DPF via the jack "1 x R".

After the start, the phases

"Pause" - "Compute" - "Hold"

are run-through only once, followed by a pause-phase being terminated by the next start instruction. This pause-phase should be at least 1 s. The time length of the phases "Pause" ( $T_p$ ) and "Compute" ( $T_R$ ) are set by means of the timers 1 and 2. The length of the phase "Hold" is approx. 15 ms, independent from the selected basic clock 1. The start instruction is given by means of a pulse of the length t, by

connecting the jack "1 x R" to binary "0" during a time  $\,$  t.

The pulse must be applied for at least 10 ms and must be terminated before start of the "Hold"-phase. After start, the indicating lamp of the push-button "Hold" will extinguish, whereas the push-button "Compute" illuminates and permits monitoring until termination of the "Hold"-phase; in the following the "Pause"push-button shortly illuminates (simulataneously, the p-control supplies binary "0"), which is again followed by the "Hold"-push-button illumination.

3.3.4. Switching Functions and External Control: "Eigen" (Self), "Fremd" (External)

These two push-buttons are used only in case of paral-Push-Buttons for Parallel lel operation of the computer with other computers having their own digital control units DBG 771, or if the control takes place via a digital computer or punched-tape control unit.

Parallel control:

After connecting the computers via respective parallel switching cables and after switch-on, the push-buttons "Fremd" (external) of all control units illuminate. By depressing the push-button "Eigen" (self) on one of the control units, the commanding unit is determined. Its "External"push-button extinguishes, whereas the "Self"push-button illuminate. With each switch-on of the total system, all computers first are set for external control, so that the commanding unit must be determined each time.

As commanding computer, always a computer with digital adapter unit should be selected.

The push-buttons of the right-hand row of the field "Control" are then only actuated on the commanding unit, i.e. the selection of operation modes, the potentiometer setting as well as testing and balancing functions are carried out centrally. The push-buttons of the parallel connected computers however also illuminate according to the entered functions. The pushbuttons of the left-hand row must be actuated on all computers of the system, according to the desired computing program.

The selection of computing elements, the value display on the digital voltmeter, a print-out of measuring values via connected printers as well as setting of the timers must be carried out separately at the different computers of a system. Setting of basic clocks and timers can be different at both control units. The central overload indication is displayed on all computers of a system in case of overload of a computing element. Independent operation of parallel-connected computers is possible only after removing the parallelconnecting cables.

External control:

For control by means of a digital computer or a punchedtape control unit, the push-button "Fremd" (external) must be depressed and in this case illuminates together with the "Self"-push-button.

3.3.5.

Notes for Push-Buttons

"Progr.", "Pot.",

"Null", "stat.", "dyn."

| Push-button<br>designation | Function                                                                             | Description<br>given in sec-<br>tion |

|----------------------------|--------------------------------------------------------------------------------------|--------------------------------------|

| "Prog."                    | 1) External program control, start of a new computing cycle can be controlled on DPF | 3.4.3.                               |

|                            | 2) Program "Single Run"                                                              | 3.3.3.                               |

| "Pot."                     | 1) Potentiometer set-<br>ting                                                        | 4.3.                                 |

|                            | 2) Setting of function<br>generators in dra-<br>wer VFG 801                          | 4.5.1.                               |

| "Null"                     | Zero-balancing of ope-<br>rational amplifier                                         | 3.6.3.                               |

| "stat."                    | Static program check                                                                 | 3.6.4.                               |

| "dyn."                     | Dynamic check. Testing of integrator capacitor and of integrator function            | 3.6.5.                               |

3.3.6. Push-Button for Overload Stop

Two large push-buttons for control of computer functions at overload of rational amplifiers are provided on the left-hand side of the control unit front plate below the Zero-instrument.

The red push-button"U" thereby serves as central overload indication for the whole system. Its function is described under 4.2.

The push-button "with hold" controls two functions, depending on the respective operation. This push-button is not interlocking.

- 1. Push-button not depressed:

The computing run is continued even in case of overload of one or several operational amplifiers. The

push-button "U" or the respective overload lamps

illuminate shortly or permanently.

- Push-button depressed (illuminated):

In case of overload the computer goes to operation

mode "Hold" independent from the selected computer

program.

Push-button " $\ddot{\text{U}}$ " and the lamps of the overload operational amplifiers than illuminate.

The computing can be again started only after depressing the push-button "Pause" and after removing the overload on the APF. Repeated start takes place by depressing the push-button "Compute".

The computing run can further be continued without depressing the push-button "Pause" by means of the push-button "with hold". In this case, however, the preset computing phase may show time errors.

3.4. Control Function of the Digital Adapter Unit This section informs about the cooperation of the digital adapter unit with the digital control unit, the output devices and the hybrid coupling unit in case the hybrid analog computer is used in combination with a digital computer within a hybrid computer system. Further explanations as to the function of the digital adapter unit are given in the following sections:

| Single control of integrators          | 4.2.3.5 |

|----------------------------------------|---------|

| Control lines of comparators           | 4.10.   |

| Replacable, digital computing elements | 4.17.   |

| Stepping switch                        | 4.18.   |

| Manual switch of DPF                   | 4.21.   |

| Binary "0", binary "12, multiple       | 4.20.   |

In the following tables, the color and position of the jacks on the digital patch panel (DPF) are listed in column DZ 772.

General determinations

1a) Assignment of the Boolean variables "0" and "1" (2"L") to the respective electrical potentials on the DPF:

(for external wiring, -1...+ 1V is required);

binary One ("1" or L) = +8...+12 V,

(for external wiring, the same values are required).

- 1b) Not wired inputs are assumed to be connected to "1".

- 1c) Static inputs are activated by "0".

- 1d) Clock inputs react on to a 1/0-change. Required height: 9V ± 1 V, steepness: 50 ns/V.

- 1e) Lamp display on card backs of freely programmable components as well as of comparator switches and of stepping switch:

The respective lamp allocated to the different components and comparator switches illuminate, if their output leads binary "1".

The lamps of the stepping switch card indicate the respective position of the switch.

### 2) Color code of digital patch panel

green: inputs of freely programmable digital elements, control input to stepping switch.

Inputs to hybrid coupling unit.

orange: outputs of freely programmable digital ele-

ments, of comparator amplifiers, of the stepping switch. Outputs of hybrid coupling

unit.

yellow: outputs of clocks, timers, control outputs.

white: control inputs to peripheral devices. Free

diodes, multiples, cross-connection lines.

red: binary "1".

blue: special control inputs to digital control

unit.

brown: control inputs of switches (integrator con-

trol switch, comparator switch. Free com-

puter control, manual switch.

black: binary "0" and not occupied jacks.

3.4.1.

Push-Buttons of Digital

Adapter Unit Stop,

Run, Lö, HT

The two push-buttons Run and Stop influence the yellow jack row WT. Push-button Run thereby supplies a clock being selected via the rotary switch. The Stop push-button interrupts this clock. The operation mode is indicated by illumination of the respective push-button (see also 3.4.2.1.4.

The push-button Lö is used for clearing the digital elements FF, ZL 2 and SR 2 (see also 3.4.2.4.)

The push-button HT is provided for manual clock (see also 3.4.2.1.4., and 3.4.2.1.5.).

|            | Meaning       | Jack<br>Designa-<br>tion                     | E                                                                            | Z 77:                             | 2 -                                                      | Function                                                                                                                                                                                                            |

|------------|---------------|----------------------------------------------|------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number     | of Jacks      |                                              | Color                                                                        | Line                              | Column                                                   |                                                                                                                                                                                                                     |

| 3.4.2      | Clocks and co | ontrol signals                               | of DPF                                                                       |                                   |                                                          |                                                                                                                                                                                                                     |

| 3.4.2.1    | Clocks        |                                              |                                                                              |                                   |                                                          | All clocks are derived from the central 100 kHz generator clock of the DBG. The square-wave clock pulses have different duty cycles (IPV). 1) Between the decade spaced clocks, a time shifting of 3.5 µs is given. |

|            |               |                                              |                                                                              |                                   |                                                          | 1) IPV: IPV = T <sub>0</sub> : T <sub>1</sub> 0  -T <sub>0</sub> T <sub>1</sub>                                                                                                                                     |

| 3.4.2.1.1. | Fixed clocks  | 10 µs 100 µs 1 ms 10 ms 100 ms 1 s 0.5 s 2 s | yellow<br>yellow<br>yellow<br>yellow<br>yellow<br>yellow<br>yellow<br>yellow | 27<br>26,<br>26<br>25<br>25<br>25 | 3-4<br>1-2<br>3-4<br>1-2<br>3-4<br>1-2<br>49-50<br>49-50 | Duty cycle: symmetrical Duty cycle: 4: 1 Duty cycle: symmetrical    |

| 3.4.2.1.2. | Basic clocks  | GT 1                                         | yellow                                                                       | 28                                | 1-4                                                      | These jacks provide the basic clock 1 (GT 1) set on the DBG                                                                                                                                                         |

|            |               | GT 2                                         | yellow                                                                       | 29                                | 1-4                                                      | These jacks provide the basic clock 2 (GT 2) set on the DBG                                                                                                                                                         |

|            |               |                                              |                                                                              |                                   |                                                          |                                                                                                                                                                                                                     |

|            |               |                                              |                                                                              |                                   |                                                          |                                                                                                                                                                                                                     |

|            |                                                        | Jack             | DZ     | 772        |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|--------------------------------------------------------|------------------|--------|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number     | Meaning<br>of Jacks                                    | Designa-<br>tion | Color  | Line       | Column   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |