Miniac

ANALOG/HYBRID COMPUTING SYSTEM

REFERENCE HANDBOOK

### **CONTENTS**

# PART I — FAMILIARIZATION AND GENERAL OPERATION (FOR ALL USERS)

|        | •                                     |       |      |       |     |  | Page   |

|--------|---------------------------------------|-------|------|-------|-----|--|--------|

| CHAPTE | R 1 - INTRODUCTION                    | <br>  |      |       |     |  | . 1-1  |

| 1.1    | THE EAI MiniAC                        | <br>  |      |       |     |  | . 1-1  |

| 1.2    | PURPOSE OF MANUAL                     | <br>  |      |       |     |  | . 1-1  |

| 1.3    | STRUCTURE OF MANUAL                   | <br>  |      |       |     |  | . 1-1  |

| 1.4    | HOW TO USE THIS MANUAL                | <br>  |      | <br>• |     |  | . 1-2  |

| CHAPTE | R 2 – MACHINE ORGANIZATION            | <br>  |      |       |     |  | . 2-1  |

| 2.1    | INTRODUCTION                          | <br>  |      |       | . , |  | . 2-1  |

| 2.2    | THE ANALOG COMPONENTS                 |       |      |       |     |  | . 2-1  |

| 2.3    | THE LOGIC COMPONENTS                  | <br>• |      |       |     |  | . 2-3  |

| 2.4    | THE ANALOG/LOGIC INTERFACE COMPONENTS | <br>• |      |       | • 4 |  | . 2-5  |

| 2.5    | THE CONTROL AND MONITORING SYSTEMS    |       |      |       |     |  | . 2-5  |

| 2.6    | THE PATCH PANEL                       |       |      |       |     |  | . 2-5  |

|        | 2.6.1 Introduction                    | <br>  |      |       |     |  | . 2-5  |

|        | 2.6.2 Patch Panel Layout              |       |      |       |     |  | . 2-5  |

| 2.7    | DVM AND COEFFICIENT POT PANEL         |       |      |       |     |  | . 2-9  |

| 2.8    | VFG PANEL                             |       |      |       |     |  | . 2-10 |

| 2.9    | THE ANALOG CONTROL PANEL              |       |      |       |     |  | . 2-10 |

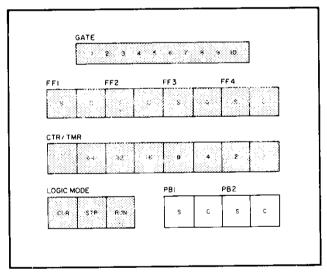

| 2.10   | THE LOGIC CONTROL PANEL               |       |      |       |     |  | . 2-14 |

| 2.11   | SETUP SWITCH/OVERLOAD INDICATOR PANEL |       |      |       |     |  | . 2-16 |

|        | 2.11.1 Introduction                   |       |      |       |     |  | . 2-16 |

|        | 2.11.2 The Identification Strip       | <br>- | <br> |       |     |  | . 2-16 |

|        | 2.11.3 The Setup Switches             |       | <br> |       |     |  | . 2-16 |

|        | 2.11.4 Amplifier Balance Controls     |       | <br> |       |     |  | .2-18  |

|        | 2.11.5 The Overload Indicators        |       | <br> |       |     |  | .2-18  |

| 2.12   | EXTERNAL CONNECTIONS                  |       | <br> |       |     |  | . 2-18 |

|                 | •                                                | Page  |

|-----------------|--------------------------------------------------|-------|

| CHAPTER 3       | - GENERAL SYSTEM OPERATIONS                      | 3-1   |

| 3.1             | INTRODUCTION                                     | 3-1   |

| 3.2             | APPLYING POWER                                   | 3-1   |

| 3.3             | PATCH PANEL INSTALLATION AND REMOVAL             | 3-1   |

| 3.4             | RUNNING A TYPICAL PROBLEM                        | 3-2   |

|                 | 3.4.1 Introduction                               | 3-2   |

|                 | 3.4.2 Preliminary Procedure                      | 3-2   |

|                 | 3.4.3 Analog Initializing Procedures             | 3-2   |

|                 | 3.4.4 Logic Initializing Procedures              | 3-3   |

| . •             | 3.4.5 Testing the Problem                        | 3-3   |

|                 | 3.4.6 Dynamic Solution                           | 3-3   |

| 3.5             | RECORDING PROCEDURES                             | 3-4   |

|                 | 3.5.1 Static Readout                             | 3-4   |

|                 | 3.5.2 Dynamic Recording and Monitoring           | 3-4   |

| 3.6             | AMPLIFIER BALANCING                              | 3-4   |

| 3.7             | USING THE PROGRAM SHEET                          | 3-5   |

| PART II – USERS | S GUIDE (FOR THE INFREQUENT USER OR TRAINEE)     |       |

| CHAPTER 4       | - INTRODUCTION TO USERS GUIDE                    | 4-1   |

| . 4.1           | USERS GUIDE                                      | 4-1   |

| 4.2             | GLOSSARY OF TERMS AND COMPUTING ELEMENTS         | . 4-1 |

|                 |                                                  |       |

| CHAPTER 5       | - PATCHING AND SETTING UP MATHEMATICAL FUNCTIONS | 5-1   |

| 5.1             | INTRODUCTION                                     | 5-1   |

| 5.2             | INVERSION                                        | 5-1   |

| 5.3             | SUMMATION                                        | 5-1   |

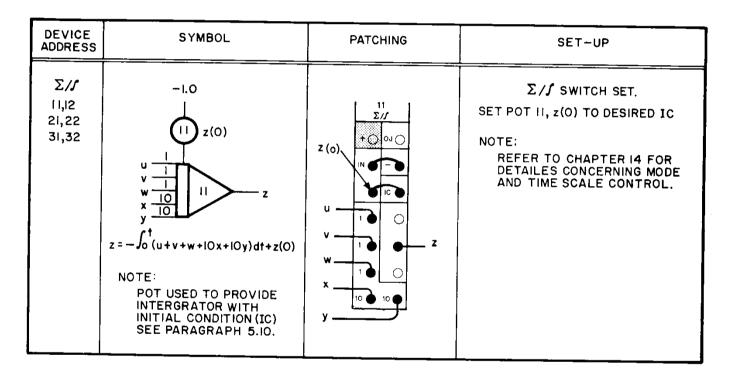

| 5.4             | INTEGRATION                                      | 5-5   |

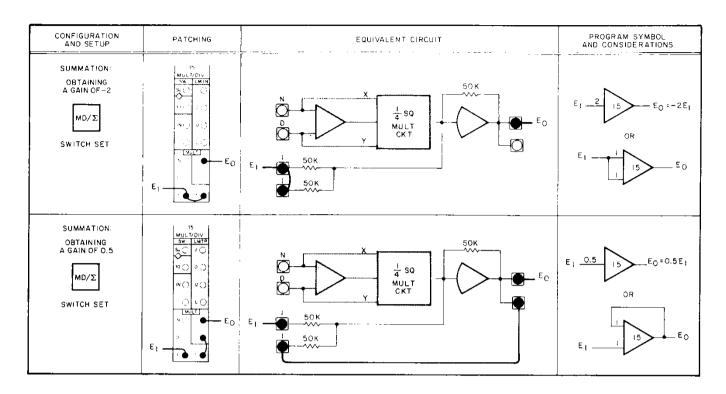

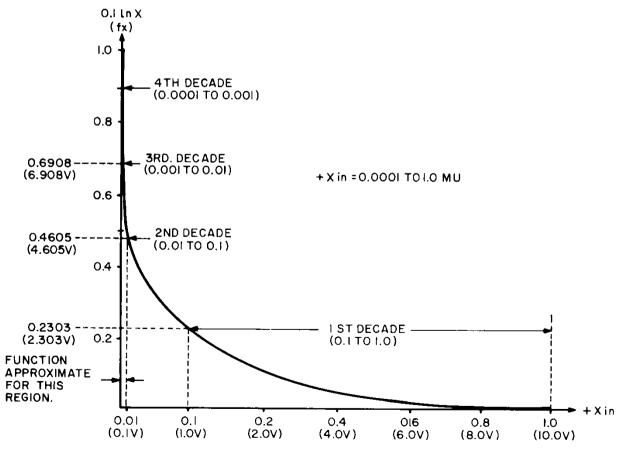

| 5.5             | MULTIPLICATION AND DIVISION                      | 5-5   |

|                 | 5.5.1 Introduction                               | 5-5   |

|                 | 5.5.2 Product of Variable and Constant           |       |

|                 | 5.5.3 Product of Two Variables                   |       |

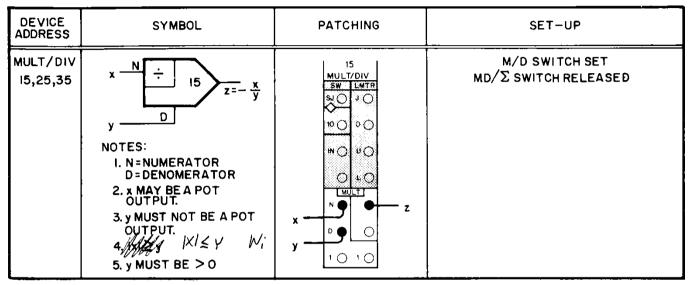

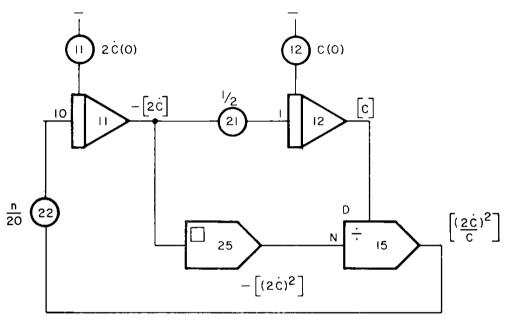

|                 | 5.5.4 Division                                   |       |

|                 |                                                  |       |

|       |         | <u> </u>                                              | age |

|-------|---------|-------------------------------------------------------|-----|

| СНУБІ | FR 5 _  | PATCHING AND SETTING UP MATHEMATICAL FUNCTIONS (Cont) |     |

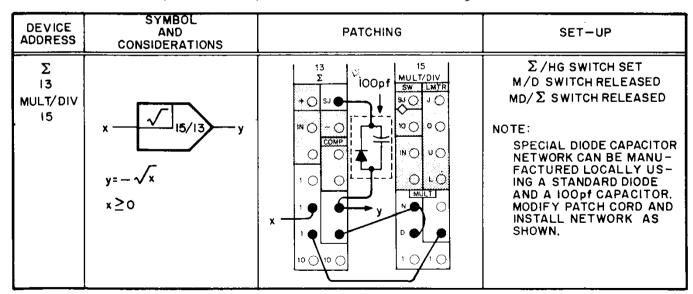

| UIAI  | 5.6     | SQUARING AND SQUARE ROOT EXTRACTION                   | 5-7 |

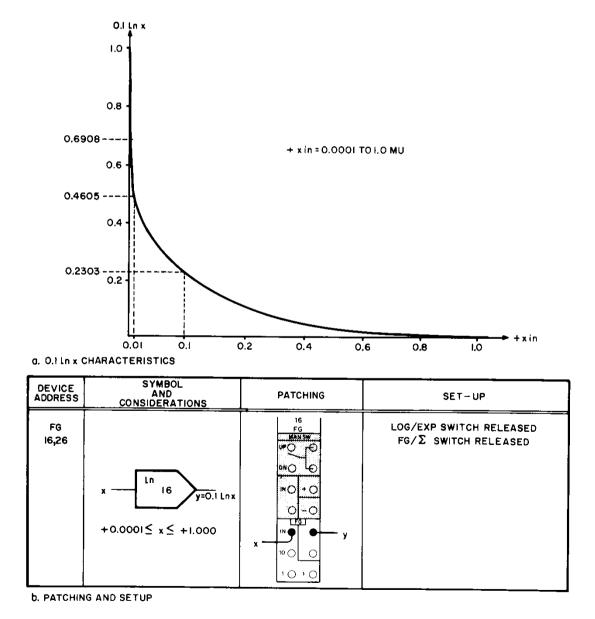

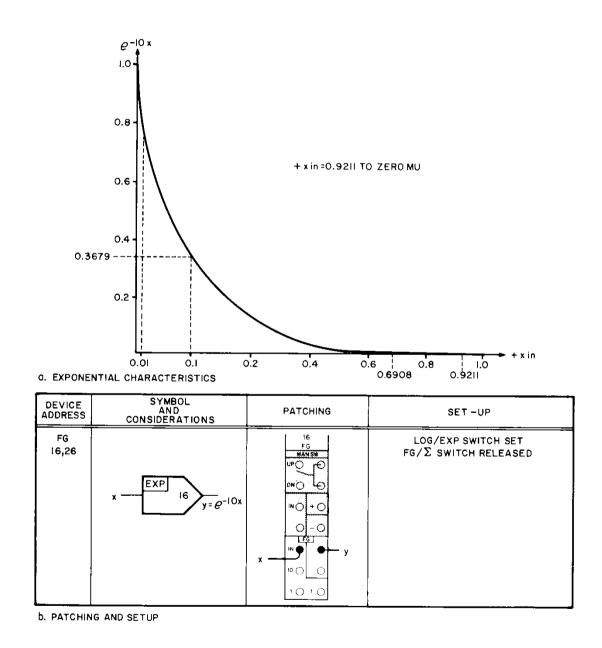

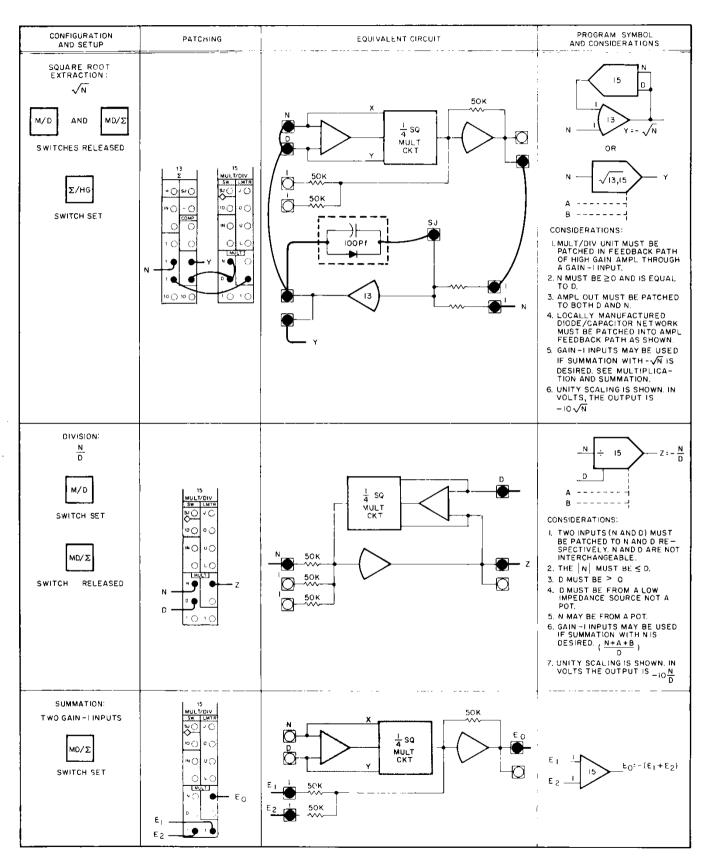

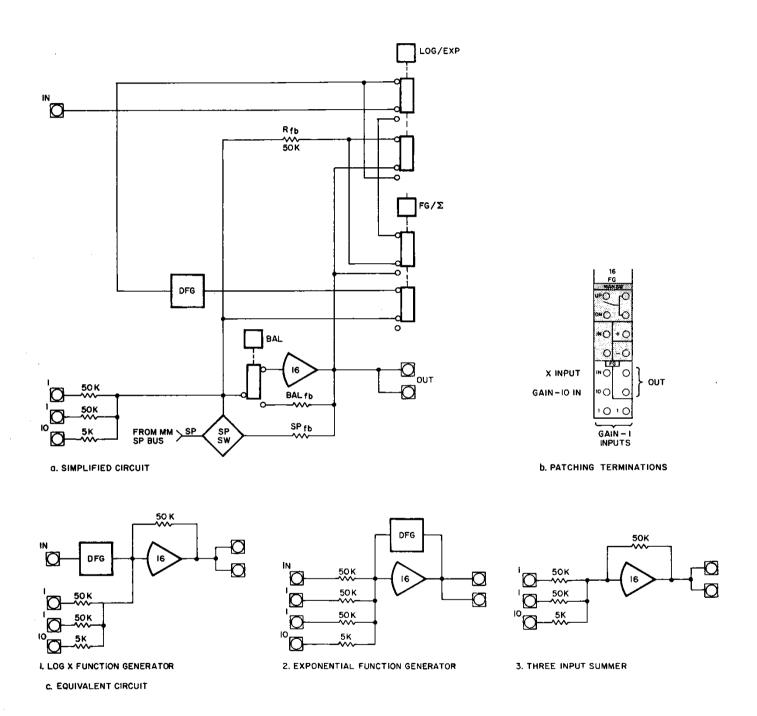

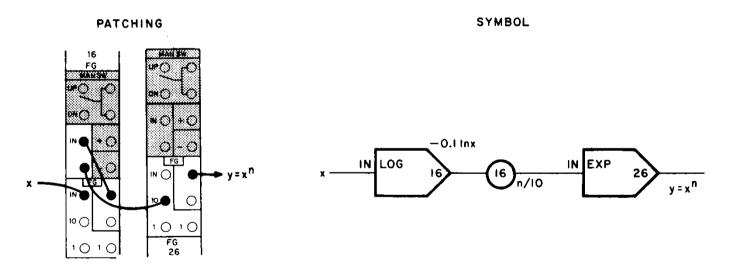

|       | 5.7     | LOGARITHMS/EXPONENTIAL FUNCTIONS (FG Devices 16, 26)  |     |

|       | 5.7     | 5.7.1 Natural Logarithm                               |     |

|       |         | 5.7.2 Exponential (e <sup>-10×</sup> )                |     |

|       | 5.8     | CONSTRAINTS (LIMITS)                                  |     |

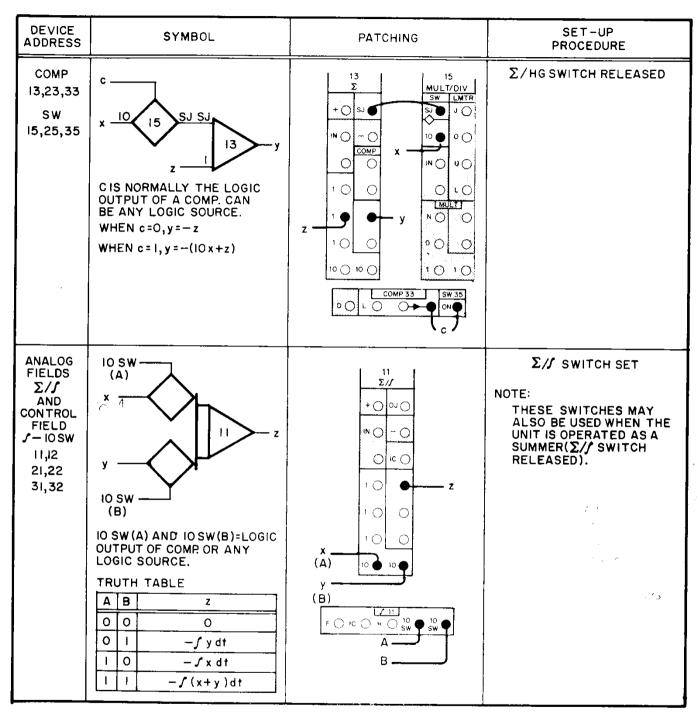

|       | 5.9     | SWITCHING FUNCTIONS                                   |     |

|       | 5.9     | 5.9.1 Manual Switching                                |     |

|       |         | 5.9.2 Automatic Switching                             |     |

|       | E 10    | CONSTANT VALUES                                       |     |

|       | 5.10    | CONSTAINT VALUES                                      |     |

| CHAP  | ΓER 6 – | - SETTING AND READING COEFFICIENT VALUES              | 6-1 |

|       | 6.1     | INTRODUCTION                                          | 6-1 |

|       | 6.2     | THE DIGITAL VOLTMETER AND POT CONTROLS                | 6-1 |

|       | 6.3     | PROCEDURE FOR SETTING A POT                           | 6-1 |

|       | 6.4     | PROCEDURE FOR READING POT VALUES                      | 6-2 |

|       |         |                                                       |     |

| CHAP. |         | - ARBITRARY FUNCTIONS FROM EMPERICAL DATA             |     |

|       | 7.1     | INTRODUCTION                                          |     |

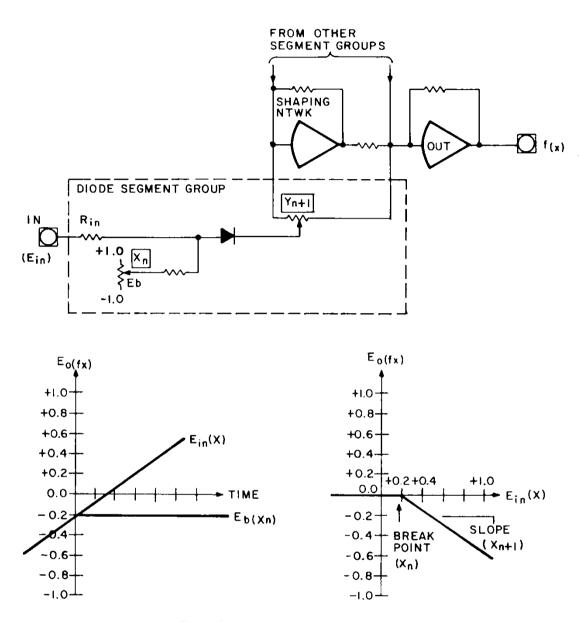

|       | 7.2     | VFG THEORY                                            |     |

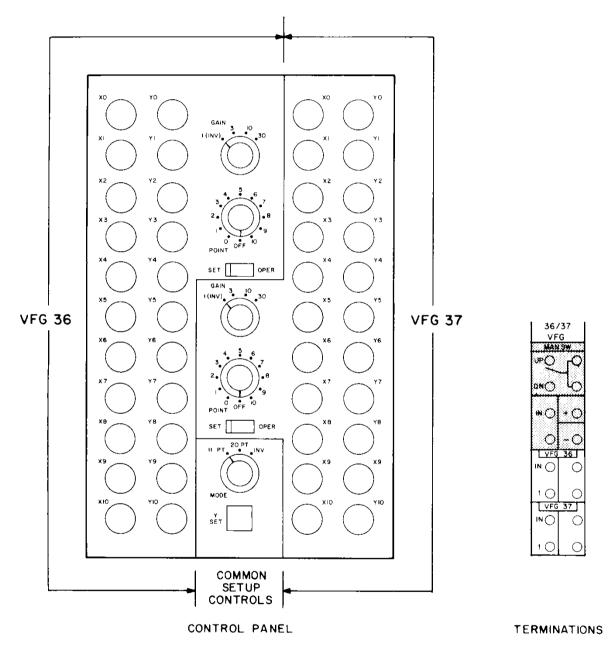

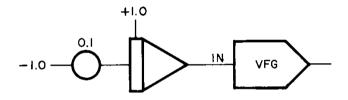

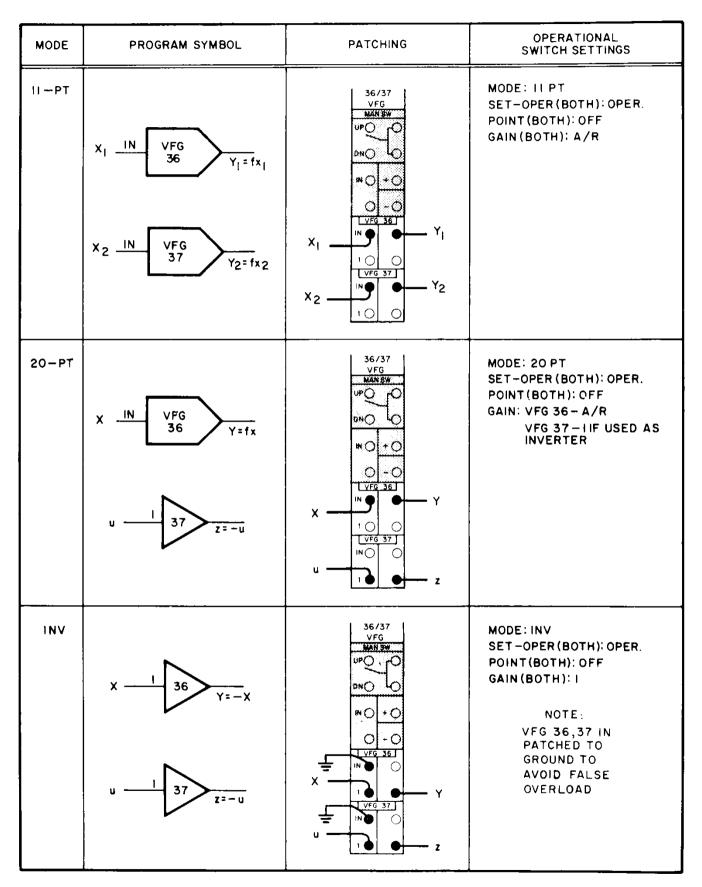

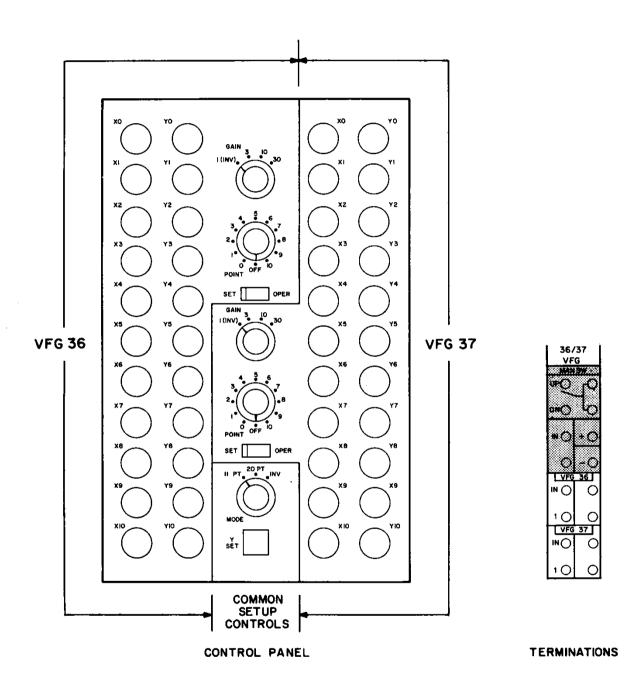

|       | 7.3     | THE VFG (Devices 36 and 37)                           |     |

|       | 7.4     | SET-UP PROCEDURE                                      |     |

|       |         | 7.4.1 11PT (10 SEGMENT) MODE                          |     |

|       |         | 7.4.2 20PT (19 SEGMENT) MODE                          |     |

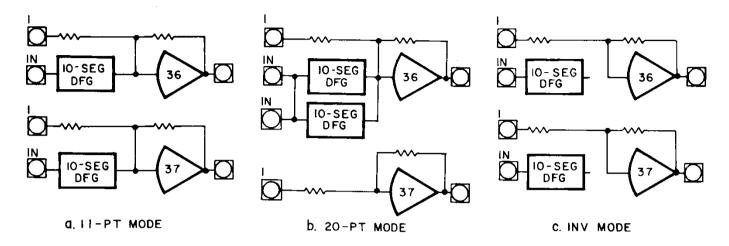

|       | 7.5     | VFG PATCHING                                          | 7-5 |

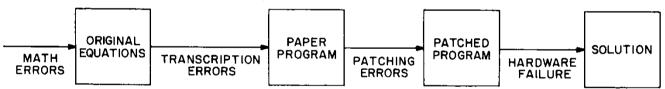

| CHAP  | TER 8 - | - CHECKING THE ANALOG PROGRAM                         | 8-1 |

| ~     | 8.1     | INTRODUCTION                                          |     |

|       | 8.2     | STATIC CHECK THEORY                                   |     |

|       | 8.3     | PROGRAM SHEET                                         |     |

|       | 8.4     | STATIC CHECK PROCEDURE                                |     |

|           |                                                                                  | Page   |

|-----------|----------------------------------------------------------------------------------|--------|

| CHAPTER 9 | ) — OBTAINING RESULTS USING AN X-Y PLOTTER                                       | . 9-1  |

| 9.1       | INTRODUCTION                                                                     | 9-1    |

| 9.2       | MiniAC TO EAI PLOTTER                                                            |        |

|           | 9.2.1 Connector Locations                                                        | , 9-1  |

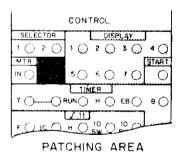

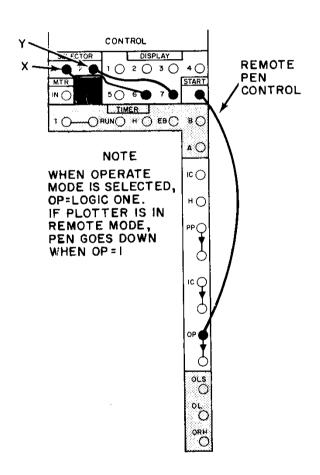

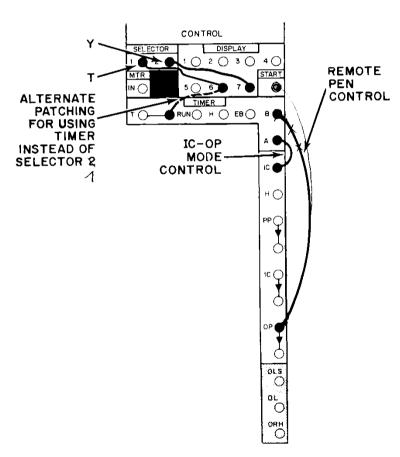

|           | 9.2.2 X Versus Y Plotting                                                        | . 9-1  |

|           | 9.2.3 Y Versus T Plotting                                                        | . 9-2  |

| 9.3       | MiniAC TO NON-EAI PLOTTER                                                        | . 9-3  |

| 9.4       | CALIBRATION                                                                      | . 9-3  |

| CHAPTER   | 10 – OBTAINING RESULTS USING AN OSCILLOSCOPE AND HIGH-SPEED REPETITIVE OPERATION | . 10-1 |

| 10.1      | INTRODUCTION                                                                     | . 10-1 |

| 10.2      | REP-OP                                                                           | . 10-1 |

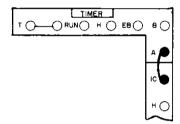

| 10.3      | B THETIMER                                                                       | . 10-1 |

| 10.4      | MiniAC TO EAI SCOPE                                                              | . 10-2 |

| 10.5      | MiniAC TO NON-EAI SCOPE                                                          | . 10-2 |

| CHAPTER   | 11 - LOGIC AND ITERATIVE OPERATION                                               | . 11-1 |

| 11.1      | INTRODUCTION                                                                     | . 11-1 |

| 11.2      | LOGIC CONTROL OF ANALOG MODES                                                    | .11-1  |

|           | 11.2.1 Overload Detection                                                        | . 11-1 |

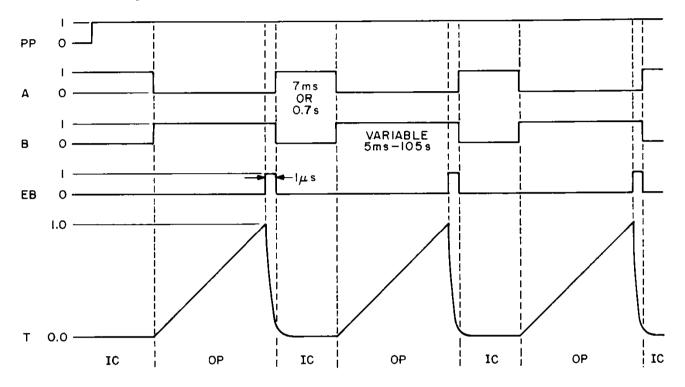

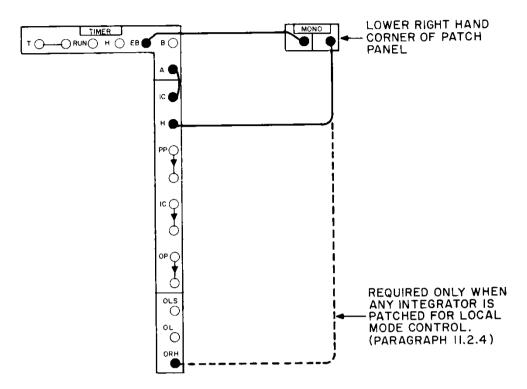

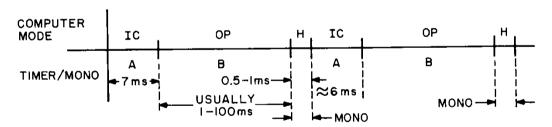

|           | 11.2.2 Three-Mode Repetitive Operation                                           | . 11-1 |

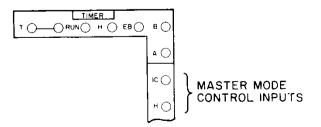

|           | 11.2.3 Master Mode Control by Logic Signals                                      | . 11-2 |

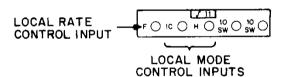

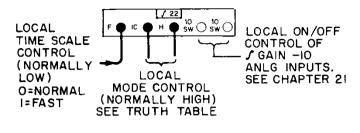

|           | 11.2.4 Local Mode Control by Logic Signals                                       | . 11-3 |

|           | 11.2.5 Mode Control Priorities                                                   | . 11-4 |

| 11.3      | B LOGIC DEVICES                                                                  | . 11-4 |

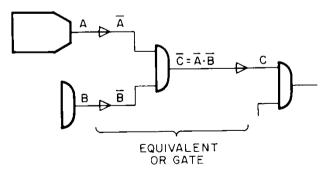

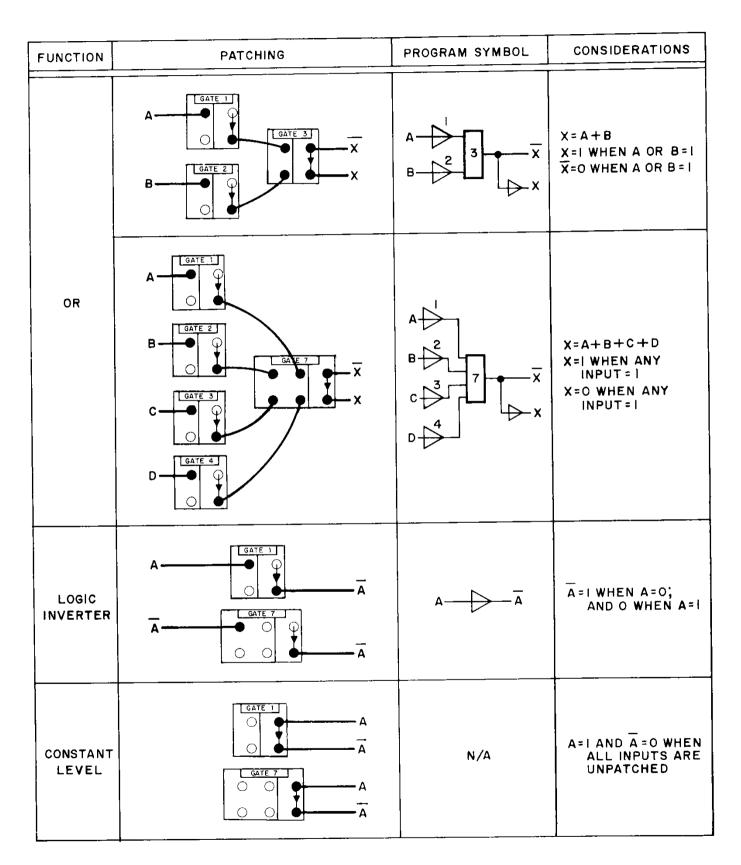

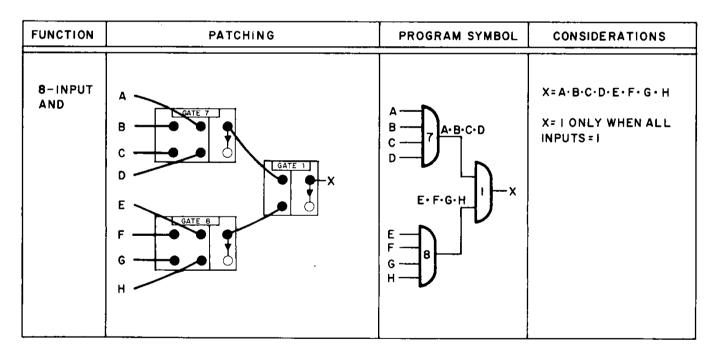

|           | 11.3.1 AND, OR, NOT Gates                                                        | . 11-4 |

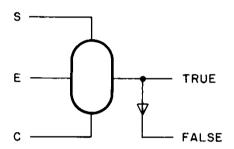

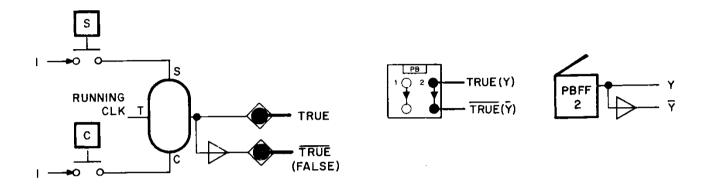

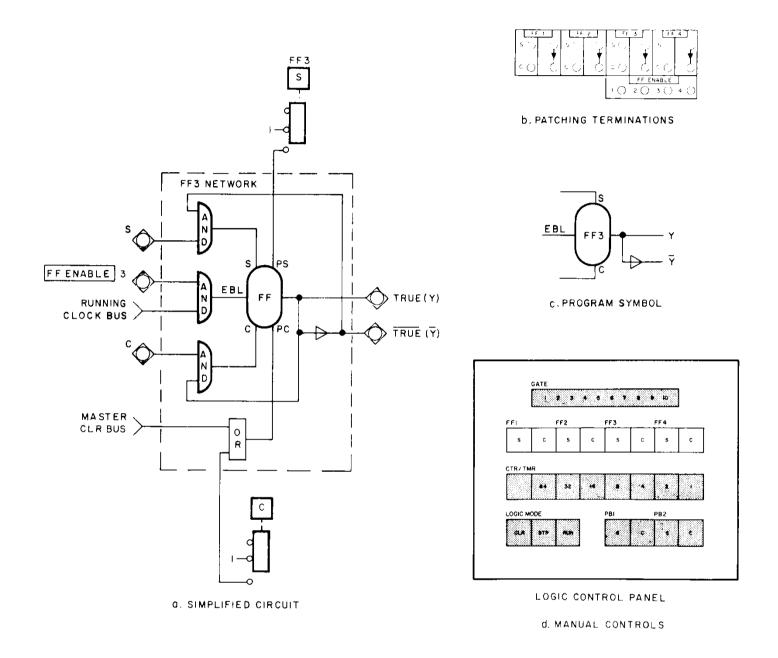

|           | 11.3.2 Flip-Flops                                                                | . 11-7 |

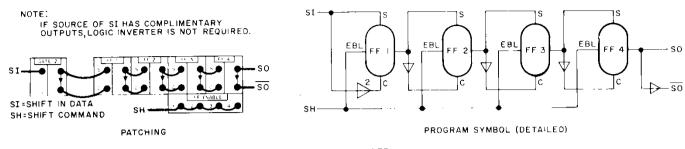

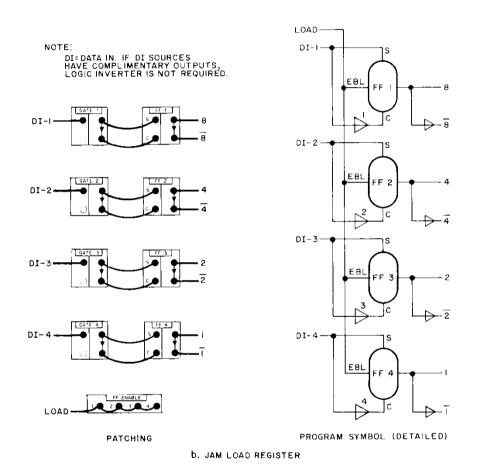

|           | 11.3.3 Shift Register                                                            | .11-9  |

|           | 11.3.4 Binary Counting                                                           | 11-11  |

|           | 11.3.5 Logic Timing                                                              | 11-12  |

|           | 11.3.6 Switching Logic Levels                                                    | 11-13  |

| 11.4      |                                                                                  |        |

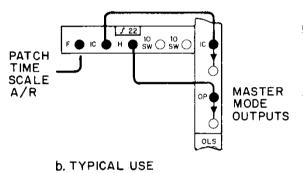

|           | 11.4.1 The T-S Unit                                                              |        |

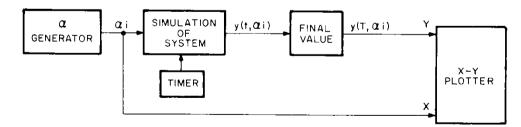

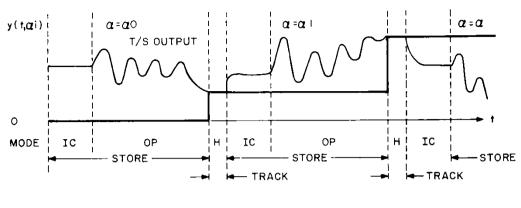

|           | 11.4.2 Parameter Sweep Program                                                   |        |

|               | Page Page                                                                         |

|---------------|-----------------------------------------------------------------------------------|

| 11.4          | ANALOG MEMORY (Cont)                                                              |

|               | 11.4.3 Parameter Implementation                                                   |

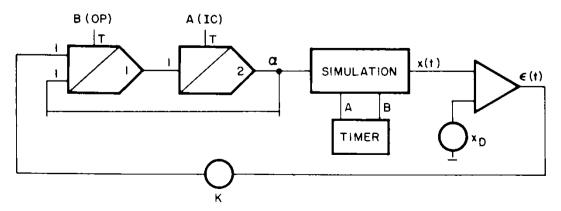

|               | 11.4.4 Boundary Value Problem                                                     |

| CHAPTER 1     | 2 - EXAMPLE OF AUTOMATIC ITERATIVE OPERATION (A TWO-POINT BOUNDARY VALUE PROBLEM) |

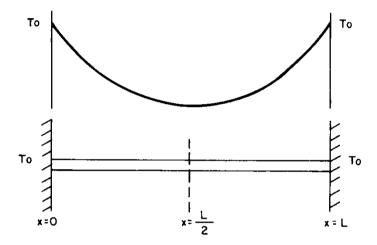

| 12.1          | THE PROBLEM STATEMENT                                                             |

|               | 12.1.1 Introduction                                                               |

|               | 12.1.2 Equations                                                                  |

|               | 12.1.3 Values                                                                     |

| 12.2          | PROCEDURE                                                                         |

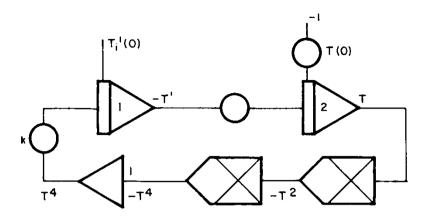

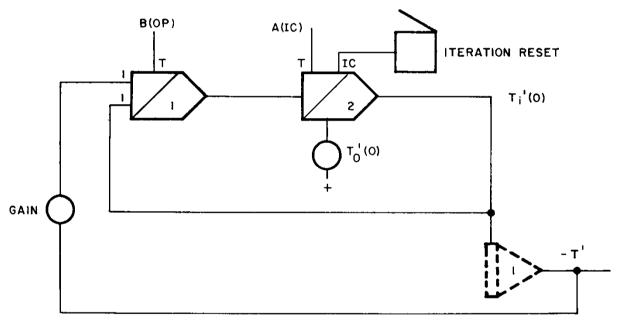

|               | 12.2.1 Preparing the Simulation                                                   |

|               | 12.2.2 Scaling                                                                    |

| 12.3          | CHECKING THE PATCHED PROGRAM                                                      |

|               | 12.3.1 Static Test                                                                |

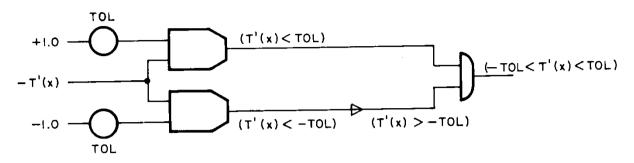

|               | 12.3.2 Logic Test                                                                 |

|               | 12.3.3 Dynamic Check                                                              |

| 12.4          | RUNNING THE PROGRAM                                                               |

| RT III – REFE | ERENCE HANDBOOK (FOR THE EXPERIENCED USER)                                        |

| CHAPTER 13    | 3 – INTRODUCTION TO REFERENCE HANDBOOK                                            |

| CHAPTER 14    | 4 – ANALOG MODE AND TIME SCALE CONTROL                                            |

| 14.1          | INTRODUCTION                                                                      |

| 14.2          | THE ANALOG MODES                                                                  |

|               | 14.2.1 Set Pot (SP)                                                               |

|               | 14.2.2 Initial Condition (IC)                                                     |

|               | 14.2.3 Hold (H)                                                                   |

|               | 14.2.4 Operate (OP)                                                               |

|               | 14.2.5 Override Hold (ORH)                                                        |

| 14.3          | THE TIME SCALES                                                                   |

| 14.4          | PUSHBUTTON MODE AND TIME SCALE CONTROL                                            |

|               |                                                                                   |

|      |        |                                                    | Page   |

|------|--------|----------------------------------------------------|--------|

| СНАР | TER 14 | - ANALOG MODE AND TIME SCALE CONTROL (Cont)        |        |

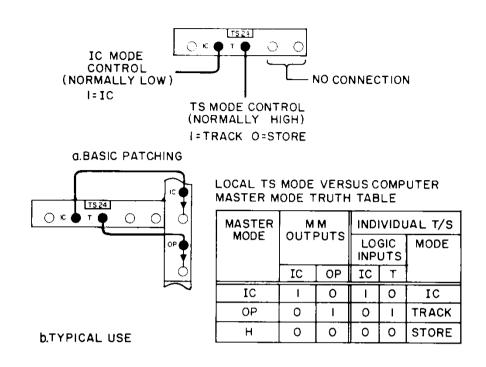

|      | 14.5   | PATCH PANEL MASTER MODE CONTROL                    | . 14-3 |

|      |        | 14.5.1 General Operation                           | . 14-3 |

|      |        | 14.5.2 The Input Control Terminations              | . 14-3 |

|      |        | 14.5.3 The Output Terminations                     | . 14-4 |

|      |        | 14.5.4 Selecting Patch Panel Mode Control          | .14-4  |

|      |        | 14.5.5 Repetitive Operation                        | .14-4  |

|      |        | 14.5.6 Iterative Operation                         |        |

|      |        | 14.5.7 Override Hold and Overload Store Operations | . 14-6 |

|      | 14.6   | LOCAL PATCH PANEL CONTROL                          | . 14-9 |

|      |        | 14.6.1 Introduction                                |        |

|      |        | 14.6.2 Local Control of Integrators                | .14-9  |

|      |        | 14.6.3 Local Control of T-S Amplifiers             | 14-10  |

|      | 14.7   | COMPUTER SLAVING AND ANALOG TRUNKS                 | 14-11  |

| СНАР | TER 15 | - LOGIC CLOCK AND LOGIC MODE CONTROL               | . 15-1 |

|      | 15.1   | INTRODUCTION                                       | . 15-1 |

|      | 15.2   | THE LOGIC MODES                                    | . 15-1 |

|      |        | 15.2.1 Run                                         | . 15-1 |

|      |        | 15.2.2 Stop/Step (STP)                             | . 15-1 |

|      |        | 15.2.3 Clear (CLR)                                 | . 15-1 |

|      | 15.3   | LOGIC MODE CONTROL                                 | . 15-1 |

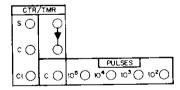

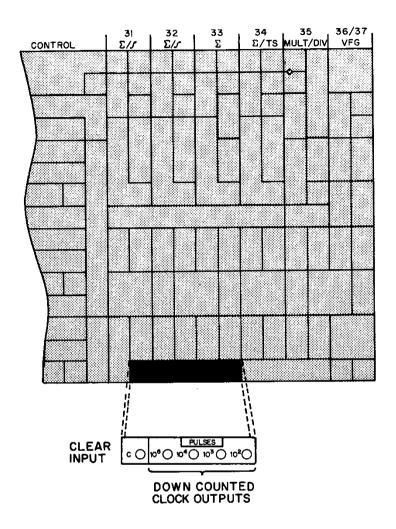

|      | 15.4   | THE CLOCK DOWNCOUNTER (PULSES)                     | .15-2  |

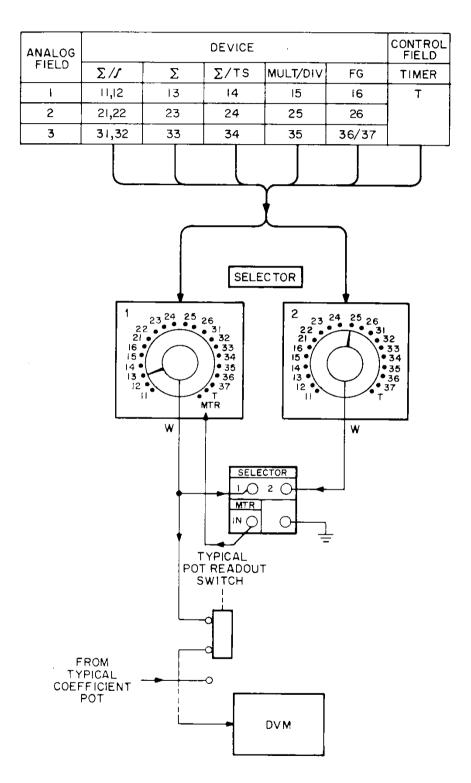

| CHAP | TER 16 | - THE SIGNAL SELECTOR                              | . 16-1 |

|      | 16.1   | INTRODUCTION                                       | . 16-1 |

|      | 16.2   | READOUT OF ADDRESSABLE COMPONENTS                  | . 16-1 |

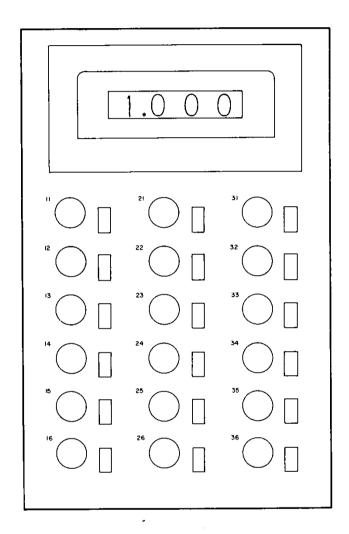

|      | 16.3   | THE DVM DISPLAY                                    | 16-2   |

|      | 16.4   | THE SELECTOR TERMINATIONS                          | . 16-2 |

|      |        | 16.4.1 Selector 1 and 2                            |        |

|      |        | 16.4.2 Selector — MTR IN                           |        |

|                   |        |                                         | Page   |

|-------------------|--------|-----------------------------------------|--------|

| СНАР              | TER 17 | - THE OVERLOAD AND STATUS INDICATORS    | . 17-′ |

|                   | 17.1   | INTRODUCTION                            |        |

|                   | 17.2   | THE OVERLOAD INDICATOR SYSTEM           |        |

|                   |        | 17.2.1 Overload Criteria                |        |

|                   |        | 17.2.2 The Overload Indicators          |        |

|                   |        | 17.2.3 Logic Level and Control          |        |

|                   | 17.3   | ANALOG STATUS INDICATORS                |        |

|                   |        | 17.3.1 Introduction                     |        |

|                   |        | 17.3.2 Comparator Indicators            |        |

|                   |        | 17.3.3 Time Scale Indicator             |        |

|                   |        | 17.3.4 Analog Mode Indicators           |        |

|                   | 17.4   | LOGIC STATUS INDICATORS                 |        |

| CHAP              | TER 18 | - COEFFICIENT POTENTIOMETER             | . 18-1 |

|                   | 18.1   | LOCATION AND IDENTIFICATION             | . 18-1 |

|                   | 18.2   | THE POTENTIOMETER                       | . 18-1 |

|                   | 18.3   | POTENTIOMETER SET-UP AND MONITORING     | . 18-1 |

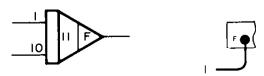

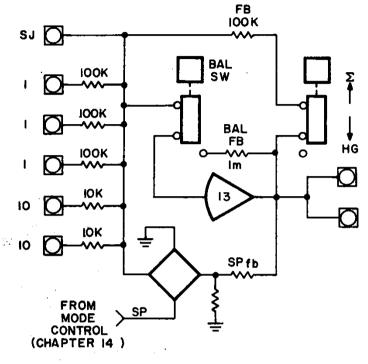

| CHAP <sup>2</sup> | TER 19 | - FIVE-INPUT SUMMER/HIGH GAIN AMPLIFIER | . 19-1 |

|                   | 19.1   | LOCATION AND IDENTIFICATION             | 19-1   |

|                   | 19.2   | THE AMPLIFIER                           | 19-1   |

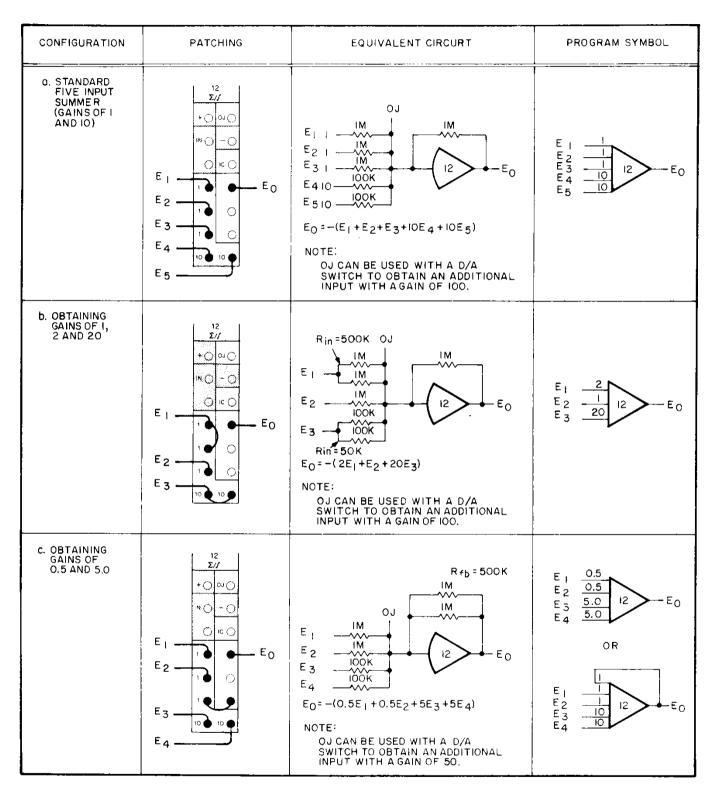

|                   | 19.3   | USED AS A SUMMER                        | 19-1   |

|                   | 19.4   | USED AS A HIGH-GAIN AMPLIFIER           | 19-1   |

| CHAP              | ΓER 20 | - SUMMER/TRACK-STORE AMPLIFIER          | 20-1   |

|                   | 20.1   | LOCATION AND IDENTIFICATION             | 20-1   |

|                   | 20.2   | THE T-S AMPLIFIER                       | 20-1   |

|                   |        | 20.2.1 Introduction                     | 20-1   |

|                   |        | 20.2.2 Mode Control                     | 20-1   |

|                   | 20.3   | USED AS A SUMMER                        | 20-3   |

|                   | 20.4   | USED AS A TRACK-STORE UNIT              | 20-3   |

|      |         |                                                 | Page   |

|------|---------|-------------------------------------------------|--------|

| CHA  | PTER 21 | I – SUMMER/INTEGRATOR                           | 21.1   |

|      | 21.1    | LOCATION AND IDENTIFICATION                     |        |

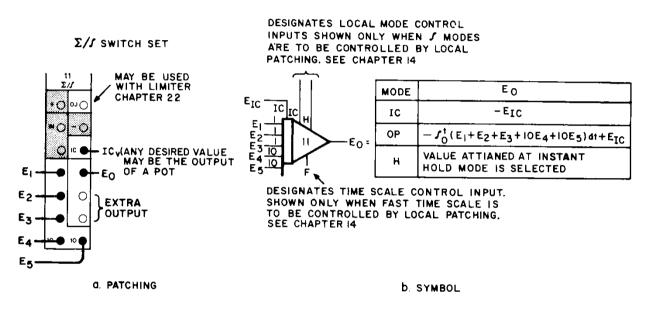

|      | 21.2    | THE SUMMER/INTEGRATOR                           |        |

|      | 21.3    | USED AS A SUMMER                                |        |

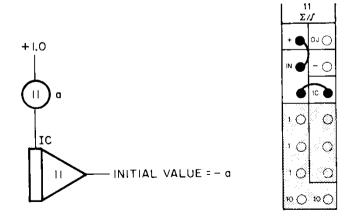

|      | 21.4    | USED AS AN INTEGRATOR                           |        |

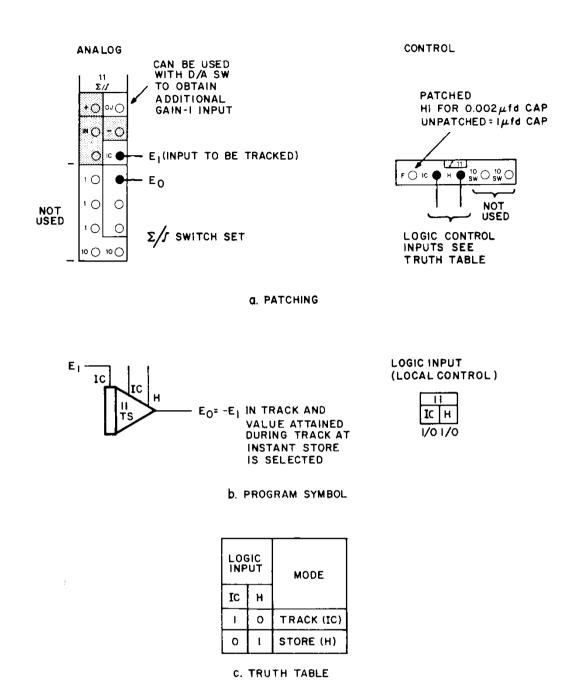

|      | 21.5    | USED AS A TRACK-STORE AMPLIFIER                 |        |

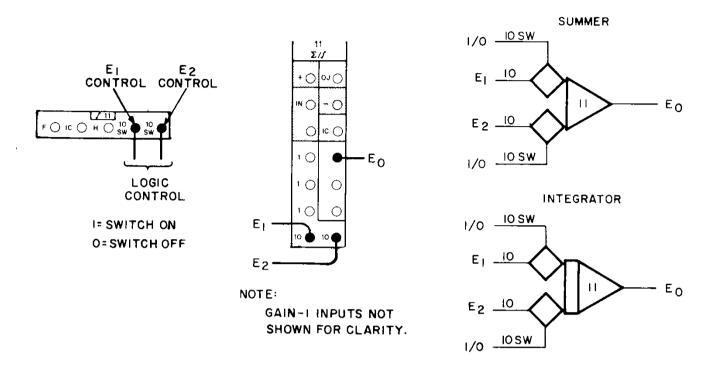

|      | 21.6    | USING THE 10 SW CONTROL INPUTS                  |        |

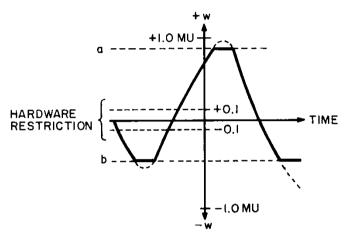

| СНАР | TER 22  | ? — LIMITERS                                    | . 22-1 |

|      | 22.1    | LOCATION AND IDENTIFICATION                     |        |

|      | 22.2    | THE FEEDBACK LIMITER                            |        |

|      | 22.3    | USING THE LIMITER                               |        |

|      |         | 22.3.1 Patching                                 |        |

|      |         | 22.3.2 Limiter Set-Up Procedure                 |        |

| СНАР | TER 23  | - MULTIPLY/DIVIDE UNIT                          | 23-1   |

|      | 23.1    | LOCATION AND IDENTIFICATION                     |        |

|      | 23.2    | THE MULTIPLIER                                  |        |

|      |         | 23.2.1 Introduction                             |        |

|      |         | 23.2.2 Multiplication, Squaring and Square Root |        |

|      |         | 23.2.3 Division                                 |        |

|      |         | 23.2.4 Summation                                | 23-1   |

|      | 23.3    | USING THE MULTIPLIER                            | 23-2   |

| СНАР | TER 24  | - LOG/EXPONENTIAL GENERATORS                    | 24-1   |

|      | 24.1    | LOCATION AND IDENTIFICATION                     |        |

|      | 24.2    | THE FUNCTION GENERATOR                          |        |

|      |         | 24.2.1 Introduction                             |        |

|      |         | 24.2.2 Logarithms                               |        |

|      |         | 24.2.3 Exponential Functions (Antilogarithms)   |        |

|      |         | 24.2.4 Summation                                |        |

|      | 24.3    | USING THE FUNCTION GENERATOR                    | _      |

|                   |        |                                                    | Page   |

|-------------------|--------|----------------------------------------------------|--------|

| СНАР              | TER 25 | - VARIABLE FUNCTION GENERATOR                      | . 25-1 |

|                   | 25.1   | LOCATION AND IDENTIFICATION                        |        |

|                   | 25.2   | THE VFG                                            |        |

|                   |        | 25.2.1 General Operation                           |        |

|                   |        | 25.2.2 Modes of Operation                          |        |

|                   |        | 25.2.3 The VFG Controls                            |        |

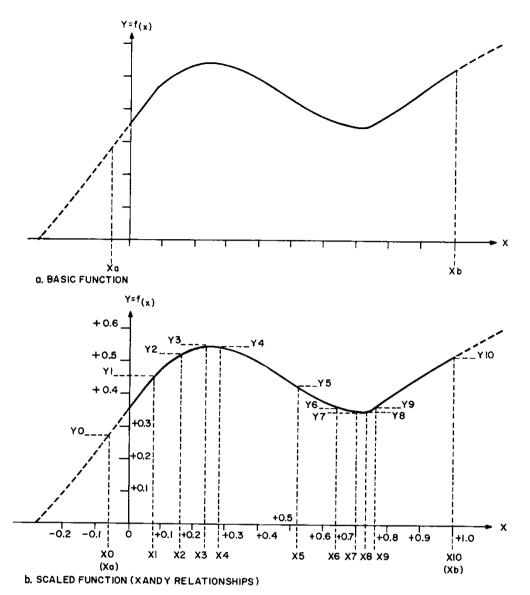

|                   | 25.3   | HOW TO SET UP THE VFG                              |        |

|                   |        | 25.3.1 Tabulating Values of X and f <sub>(x)</sub> |        |

|                   |        | 25.3.2 Determining Breakpoint Location             |        |

|                   |        | 25.3.3 VFG Setup Theory                            |        |

|                   | 25.4   | SETTING AN 11-POINT FUNCTION                       |        |

|                   |        | 25.4.1 General                                     |        |

|                   |        | 25.4.2 Preliminary Setup Procedures                |        |

|                   |        | 25.4.3 Setting X and Y                             |        |

|                   |        | 25.4.4 Insufficient Slope                          |        |

|                   |        | 25.4.5 Trimming Adjustments                        |        |

|                   | 25.5   | SETTING A 20-POINT FUNCTION                        |        |

|                   | 25.6   | PLOTTING THE FUNCTION                              |        |

|                   | 25.7   | PATCHING THE VFG INTO A PROBLEM                    |        |

|                   |        |                                                    |        |

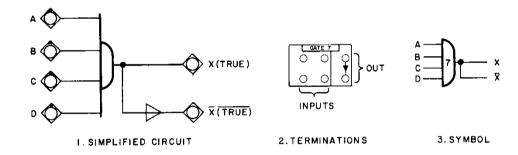

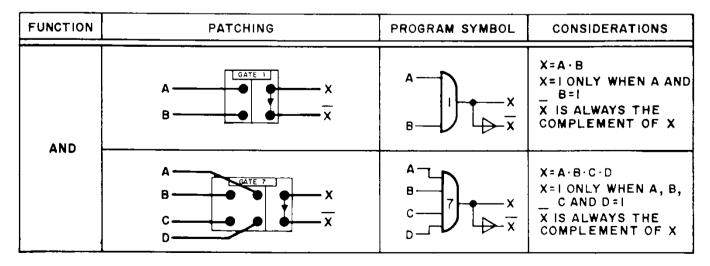

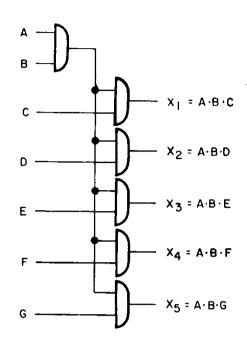

| CHAP              | TER 26 | - AND GATES                                        | . 26-1 |

|                   | 26.1   | LOCATION AND IDENTIFICATION                        |        |

|                   | 26.2   | THE AND GATE                                       | . 26-1 |

|                   | 26.3   | USING THE AND GATE                                 | . 26-1 |

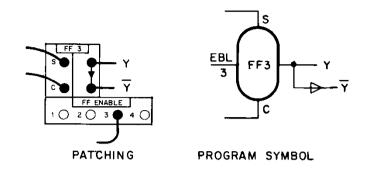

| CHAP <sup>-</sup> | TER 27 | - GENERAL PURPOSE AND PUSHBUTTON FLIP-FLOPS        | 27-1   |

|                   | 27.1   | LOCATION AND IDENTIFICATION                        |        |

|                   | 27.2   | THE PUSHBUTTON FLIP-FLOP                           |        |

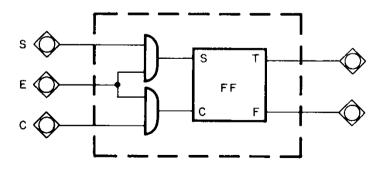

|                   | 27.3   | THE GENERAL PURPOSE FLIP-FLOP                      |        |

|                   |        | 27.3.1 General Operation                           |        |

|                   |        | 27.3.2 The Pushbutton Control                      |        |

|                   |        | 27.3.3 The Patch Panel Terminations                |        |

|                   |        |                                                    |        |

|        |        |                                                                                   | Page   |

|--------|--------|-----------------------------------------------------------------------------------|--------|

| O114 D | TED 07 | OFNEDAL BUDDOOF AND SUBJECTION TO BE ADD (S. )                                    |        |

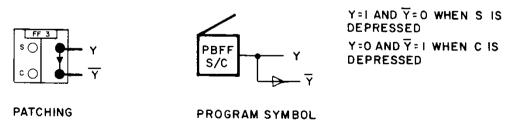

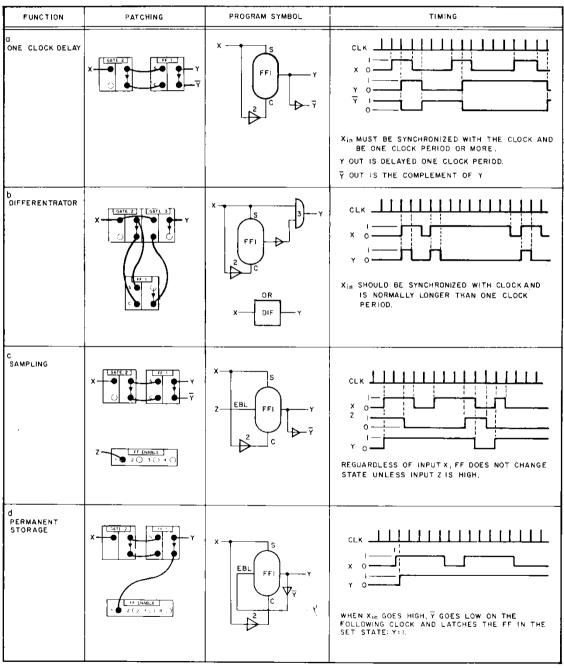

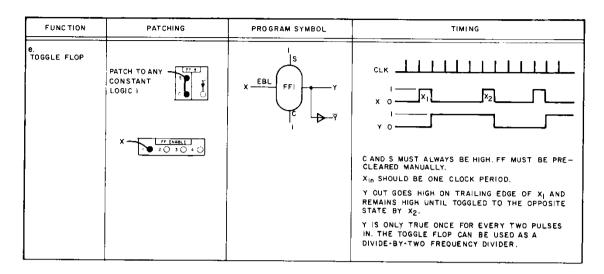

| CHAP   | 27.4   | - GENERAL PURPOSE AND PUSHBUTTON FLIP-FLOPS (Cont)  BASIC CIRCUITS USING THE GPFF | 27.2   |

|        | 27.4   |                                                                                   |        |

|        |        | 27.4.1 General Use                                                                |        |

|        |        | 27.4.2 Used to Generate a One Clock Delay                                         |        |

|        |        | 27.4.3 Used as a Differentiator                                                   |        |

|        |        | 27.4.4 Using the Latching Function                                                |        |

|        |        | 27.4.5 Used as a Flip-Flop Register                                               | . 27-6 |

| CHAP   | TER 28 | - ANALOG SWITCHES AND COMPARATORS                                                 | . 28-1 |

|        | 28.1   | LOCATION AND IDENTIFICATION                                                       | . 28-1 |

|        | 28.2   | THE MANUAL SWITCH                                                                 | . 28-1 |

|        | 28.3   | THE D/A SWITCH                                                                    |        |

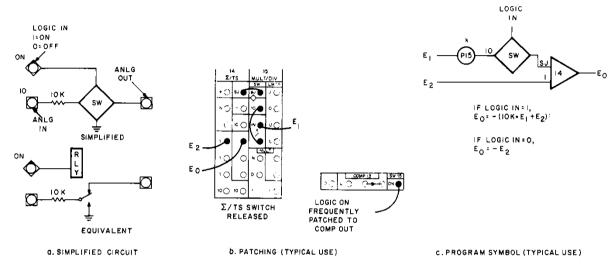

|        |        | 28.3.1 General Operation                                                          |        |

|        |        | 28.3.2 Using the D/A Switch                                                       |        |

|        | 28.4   | THE A/D COMPARATOR                                                                |        |

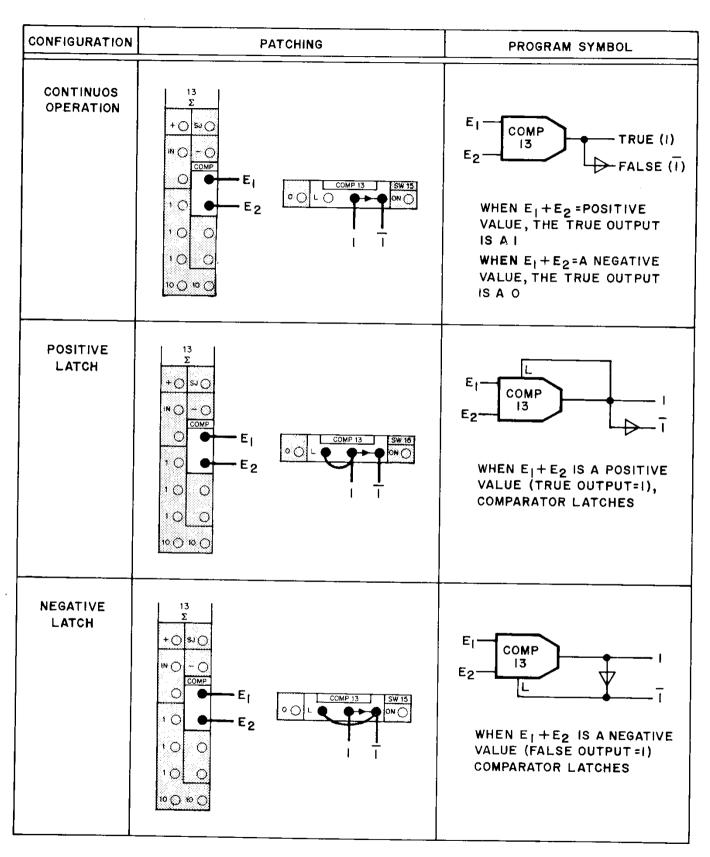

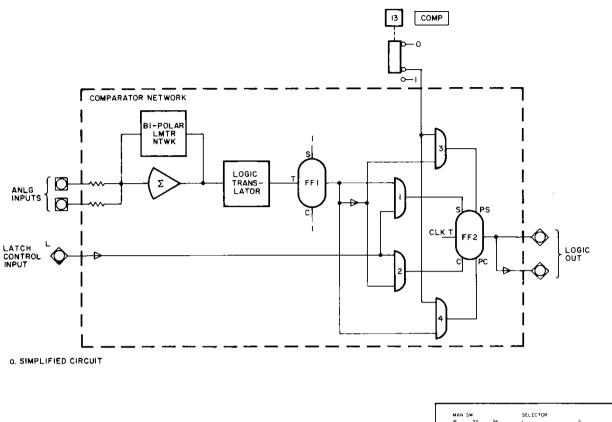

|        |        | 28.4.1 General Operation                                                          |        |

|        |        | 28.4.2 Basic Comparator Patching                                                  |        |

| СНУВІ  | FED 20 | TIMING DEVICES                                                                    |        |

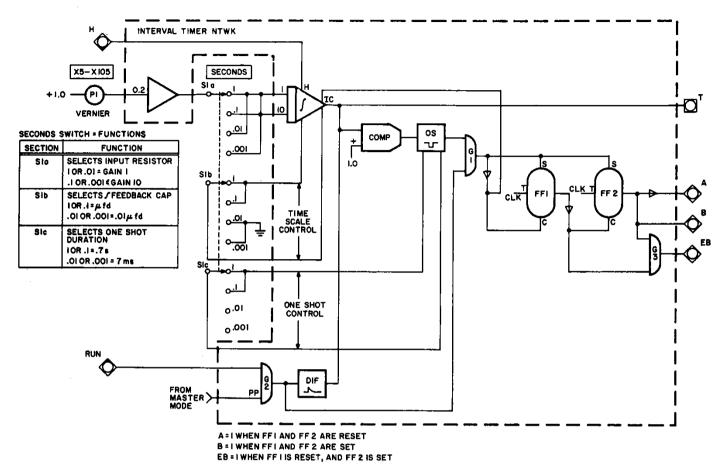

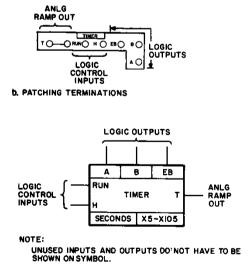

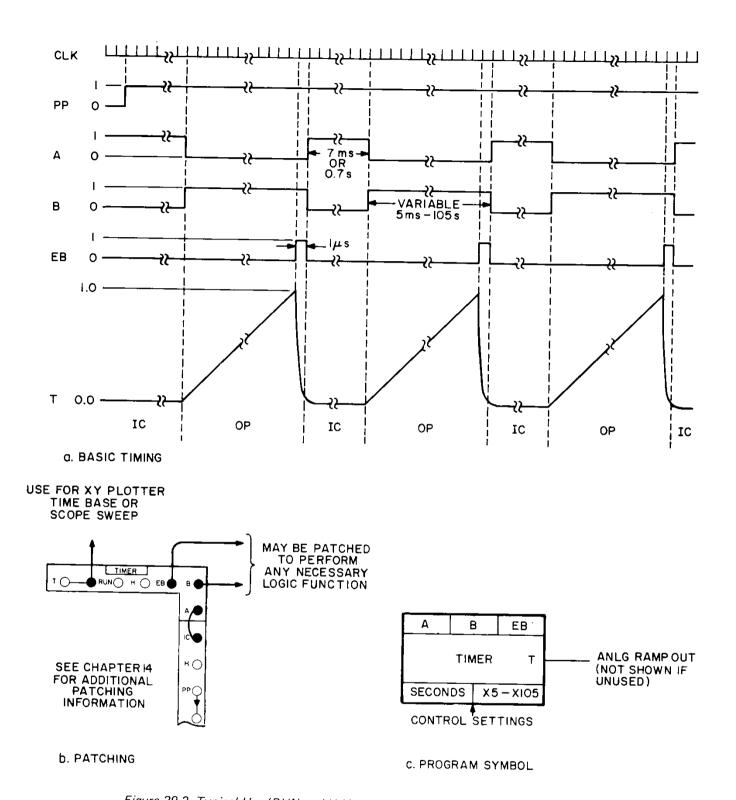

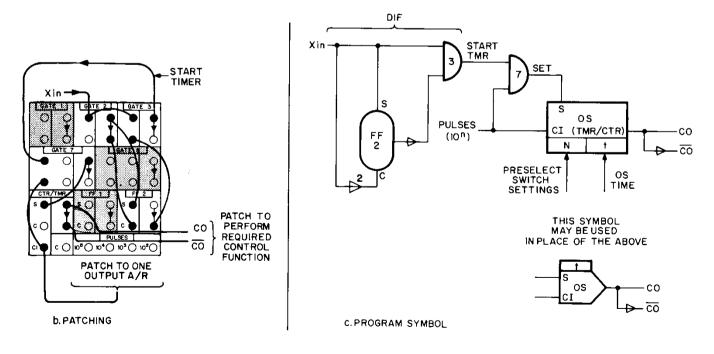

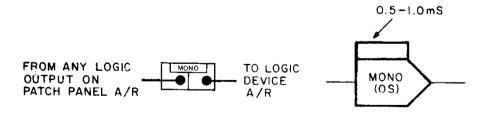

| CHAF   | 29.1   | - TIMING DEVICES                                                                  |        |

|        |        | LOCATION AND IDENTIFICATION                                                       |        |

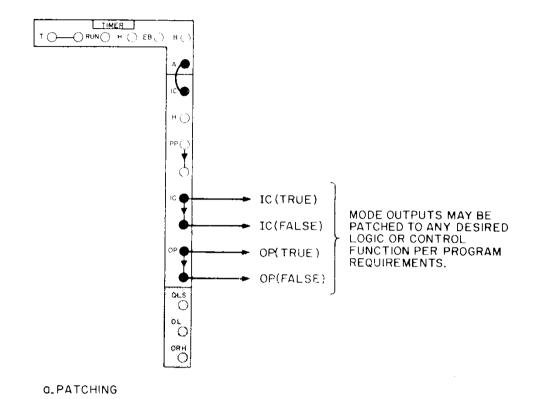

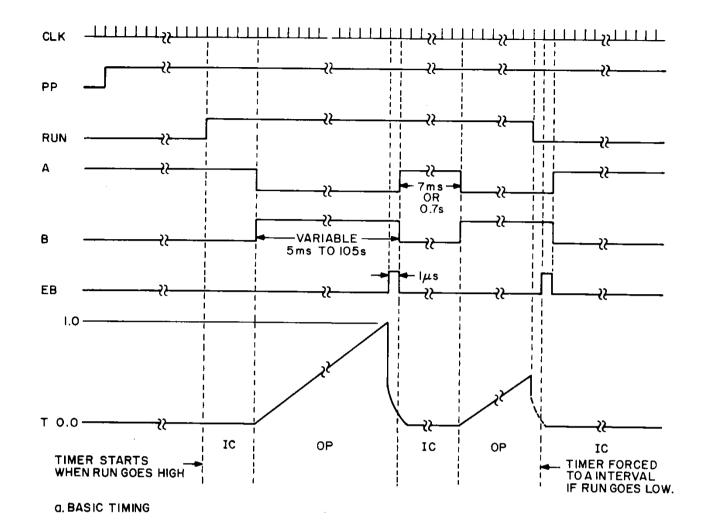

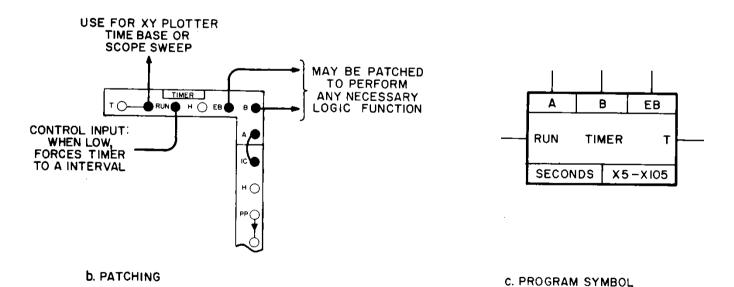

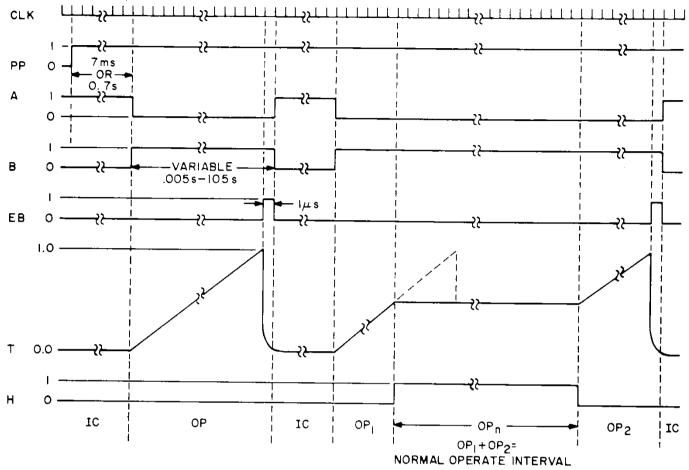

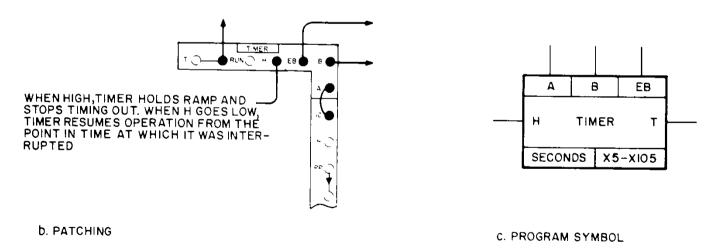

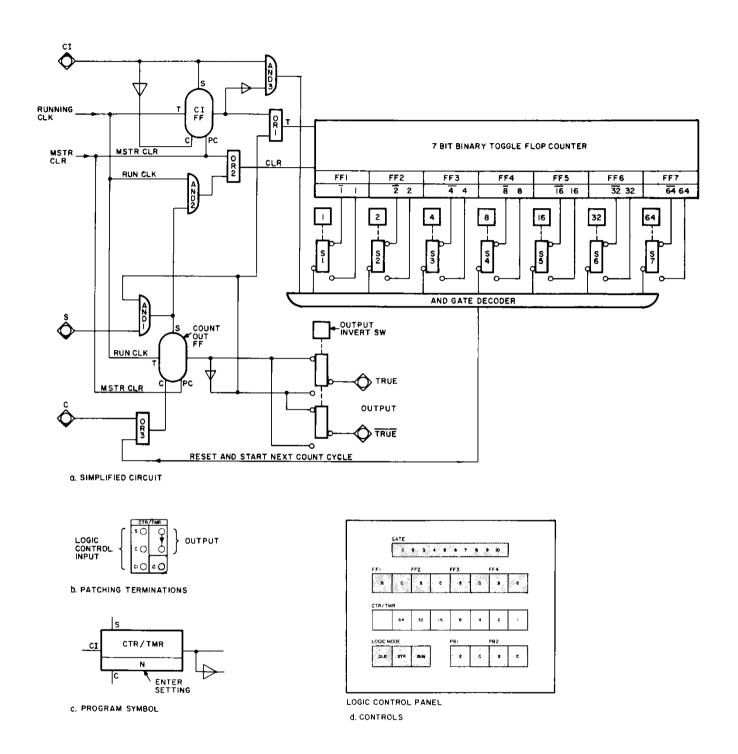

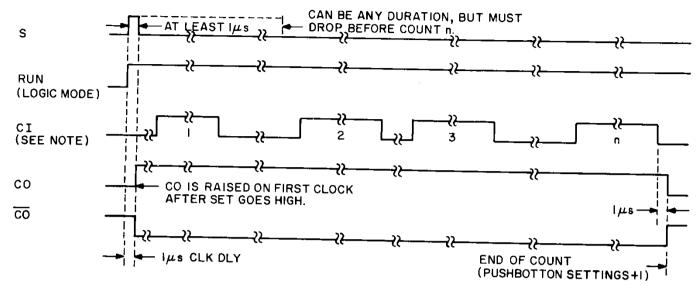

|        | 29.2   | THE INTERVAL TIMER                                                                |        |

|        |        | 29.2.1 Overall Operation                                                          |        |

|        |        | 29.2.2 The Manual Controls                                                        |        |

|        |        | 29.2.3 The TIMER Patch Panel Terminations                                         |        |

|        |        | 29.2.4 Using the Timer                                                            |        |

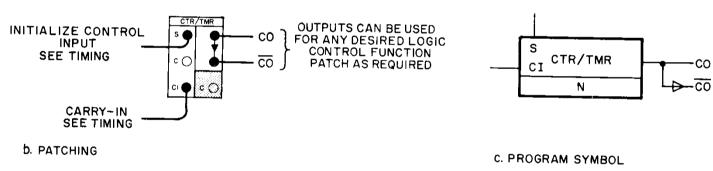

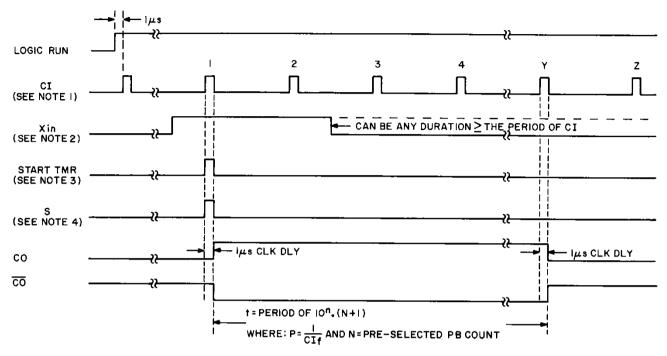

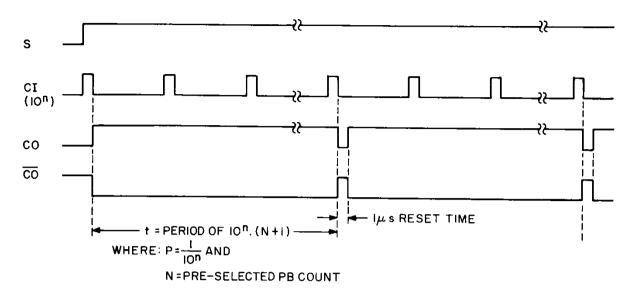

|        | 29.3   | THE COUNTER/TIMER                                                                 |        |

|        |        | 29.3.1 General Operation                                                          |        |

|        |        | 29.3.2 The Manual Controls                                                        |        |

|        |        | 29.3.3 The Patch Panel Terminations                                               | . 29-7 |

|        |        | 29.3.4 General Use                                                                | 29-9   |

|        |        | 29.3.5 Used as an Event Counter                                                   | 29-9   |

|        |        | 29.3.6 Used as an Event Monitor                                                   | 29-9   |

|        |        | 29.3.7 Used as a One-Shot                                                         | 29-10  |

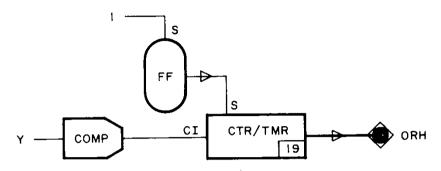

|        |        | 29.3.8 Used as a Logic Timer                                                      | 9-12   |

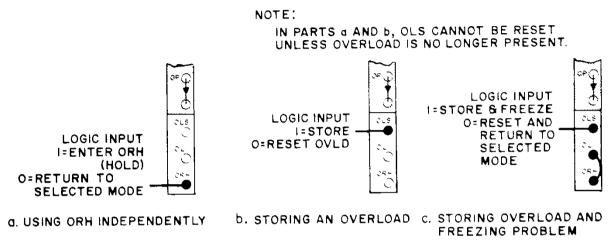

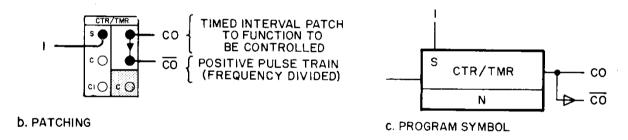

|        | 29.4   | THE MONOSTABLE MULTIVIBRATOR                                                      | 10.40  |

### **ILLUSTRATIONS**

| Figure<br>Number | Title                                                       | Page        |

|------------------|-------------------------------------------------------------|-------------|

| 1.1              | Typical MiniAC Computing System                             | 1-1         |

| 2.1              | Typical MiniAC                                              | 2-2         |

| 2.2              | The Patch Panel                                             | 2-4         |

| 2.3              | General Patching Areas                                      | 2-6         |

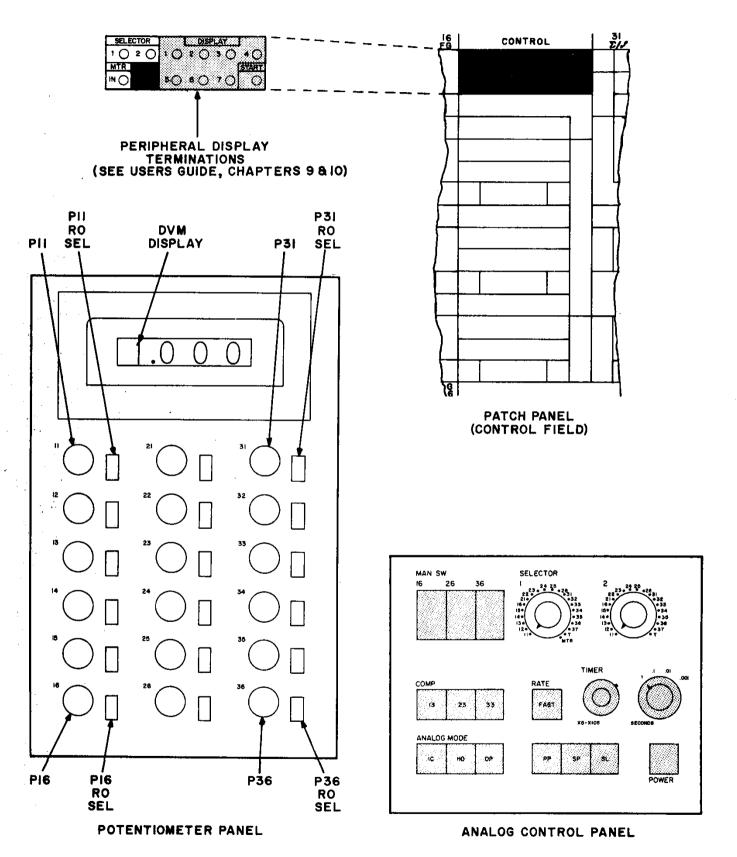

| 2.4              | DVM and Coefficient Pot Panel                               | 2-10        |

| 2.5              | Analog Control Panel                                        | 2-11        |

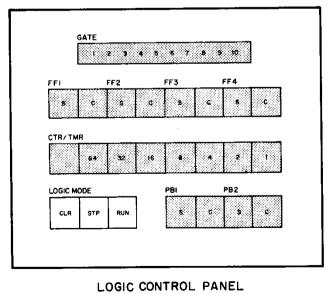

| 2.6              | Logic Control Panel                                         | 2-14        |

| 2.7              | Setup Switch/Overload Indicator Panel (Open)                | 2-16        |

| 3.1              | Program Sheet                                               | 3-7         |

| 5.1              | Inversion: Patching and Setup                               | 5-2         |

| 5.2              | Summation: Patching and Setup                               | 5-4         |

| 5.3              | Integration (With Initial Condition): Patching and Setup    | 5-5         |

| 5.4              | Multiplication of Variable and Constant: Patching and Setup | 5-6         |

| 5.5              | Multiplication of Two Variables: Patching and Setup         | 5-6         |

| 5.6              | Division: Patching and Setup                                | 5-7         |

| 5.7              | Square Root: Patching and Setup                             | 5-7         |

| 5.8              | Natural Logarithm                                           | 5-8         |

| 5.9              | Exponential Function                                        | 5-9         |

| 5.10             | Constraints: Patching and Setup                             | 5-10        |

| 5.11             | Programmed Switches: Patching and Setup                     | 5-13        |

| 6.1              | DVM and Coefficient Pot Controls                            | 6-1         |

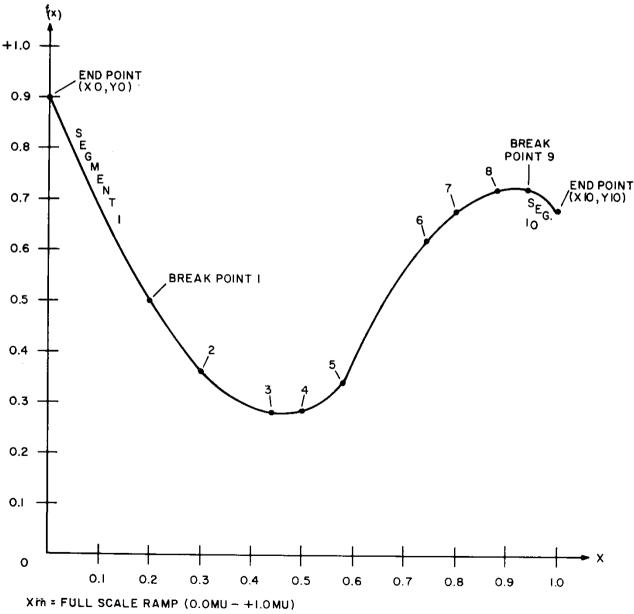

| 7.1              | Sample Arbitrary Function                                   | 7-1         |

| 7.2              | The VFG Controls                                            | 7-2         |

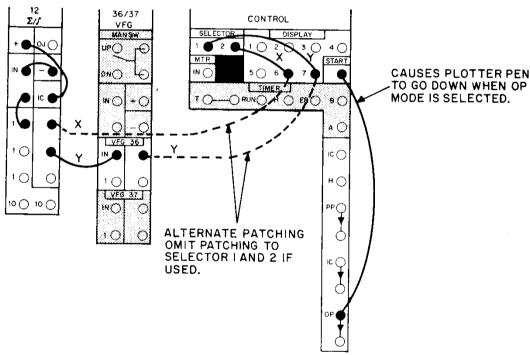

| 7.3              | Program for Plotting VFG Output                             | 7-4         |

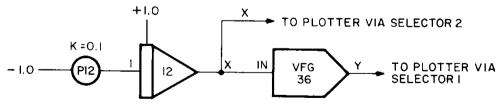

| 7.4              | VFG Patching                                                | 7-6         |

| 8.1              | The Programming Process and Possible Errors                 | 8-1         |

| 8.2              | Sample Program Sheet                                        | 8-2         |

| 8.3              | Sample Problem                                              | 8-3         |

| 8.4              | Selector: Patching Area and Controls                        |             |

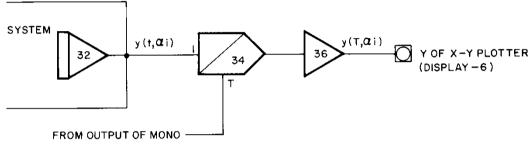

| 9.1              | Typical Patching for X Versus Y Plot                        |             |

| 9.2              | Typical Patching for Y Versus T Plot                        |             |

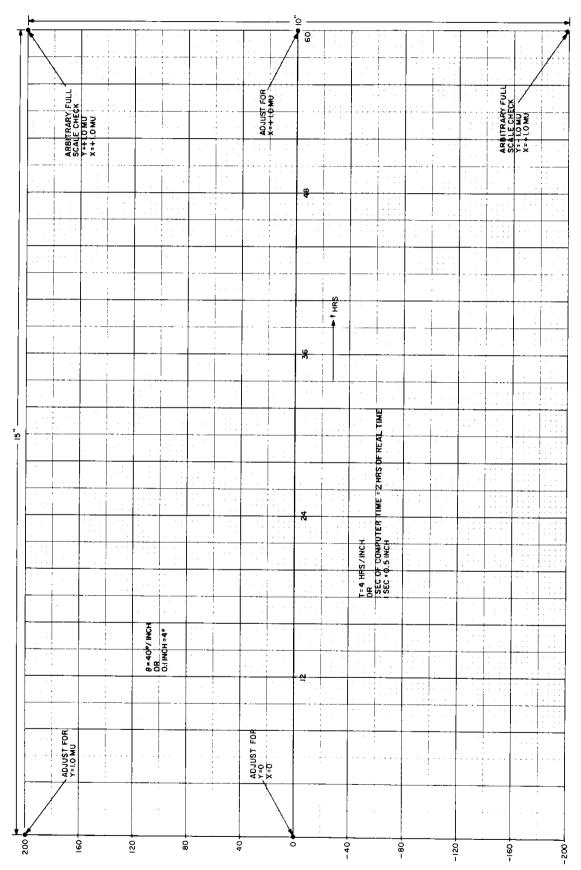

| 9.3              | Sample Plotter Calibration                                  | Q_ <i>1</i> |

### **ILLUSTRATIONS (CONT)**

| Figure<br>Number | Title                                                                                                   | Page  |

|------------------|---------------------------------------------------------------------------------------------------------|-------|

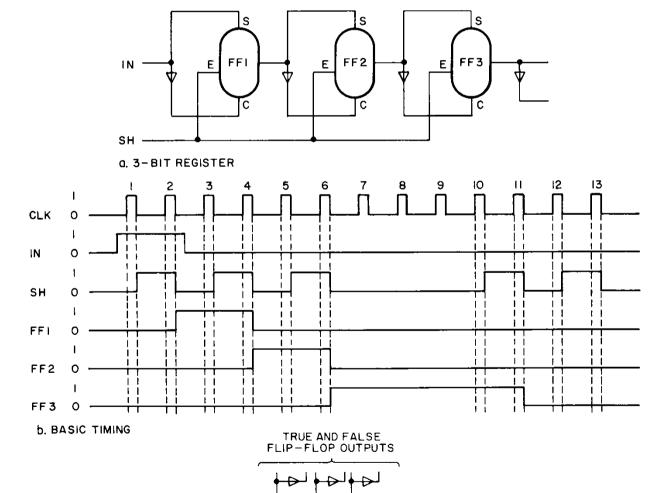

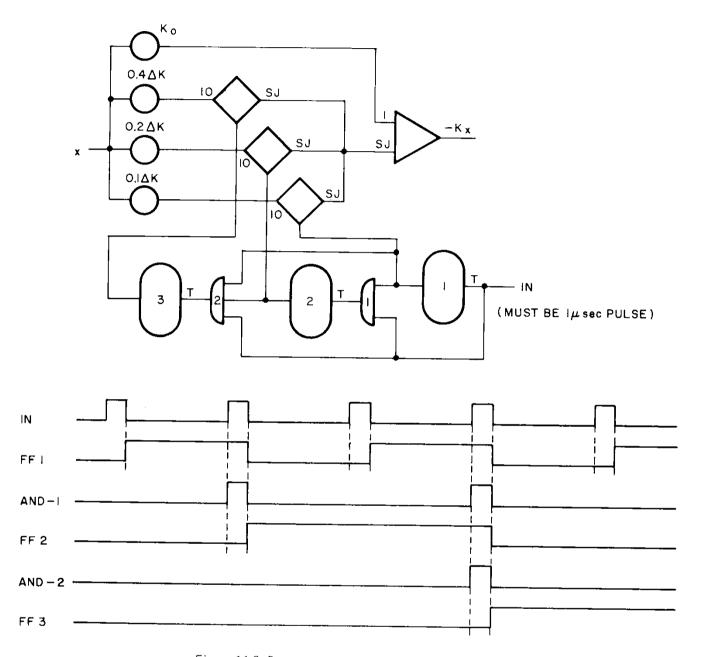

| 11.1             | Shift Register Operation                                                                                | 11-10 |

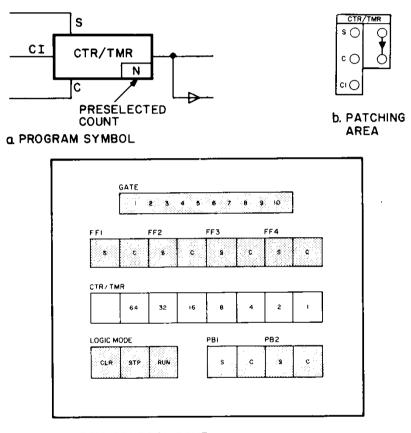

| 11.2             | Logic Counter                                                                                           | 11-11 |

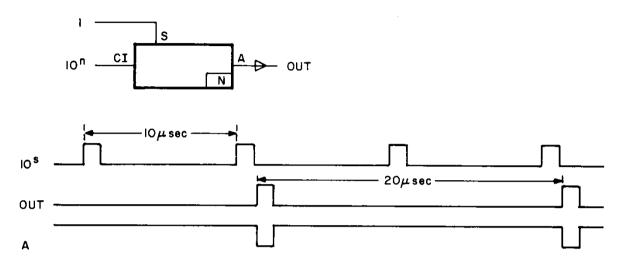

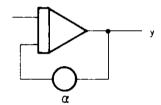

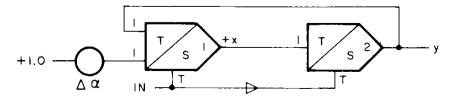

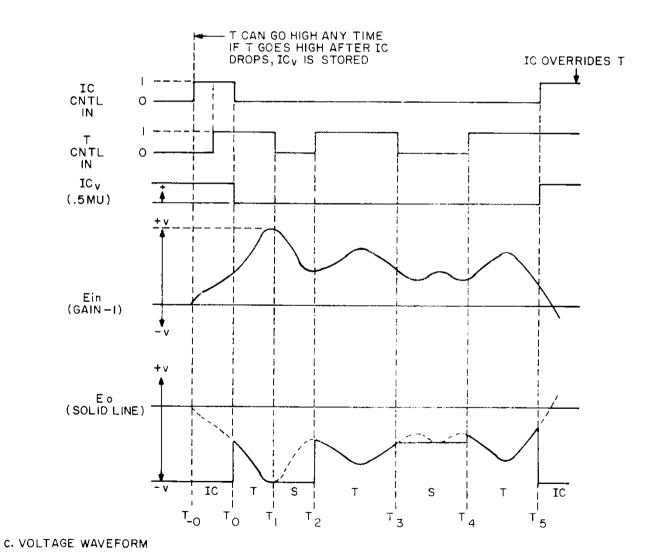

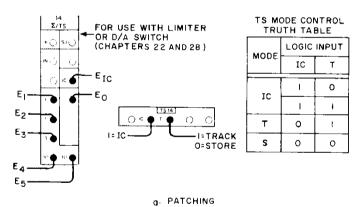

| 11.3             | The Track-Store Unit                                                                                    | 11-14 |

| 11.4             | Track-Store Behavior                                                                                    | 11-14 |

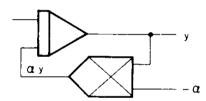

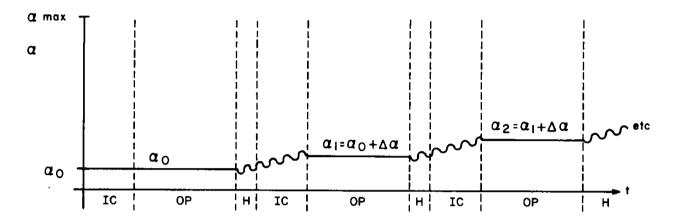

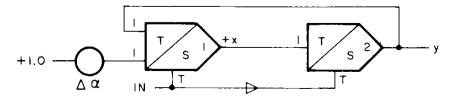

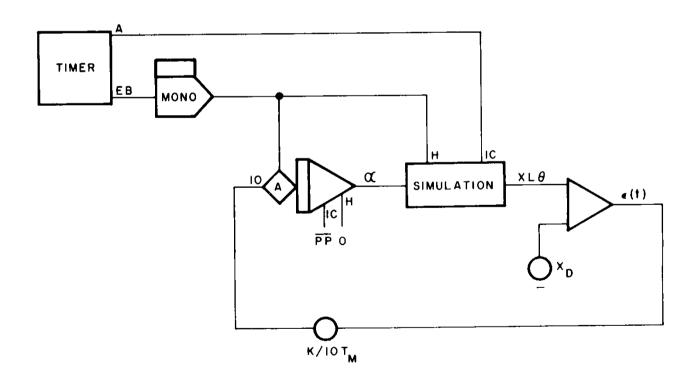

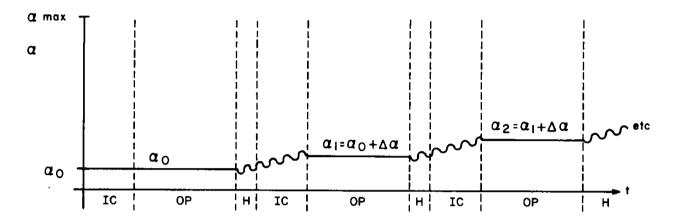

| 11.5             | Parameter Sweep: Basic Program and Waveforms                                                            | 11-16 |

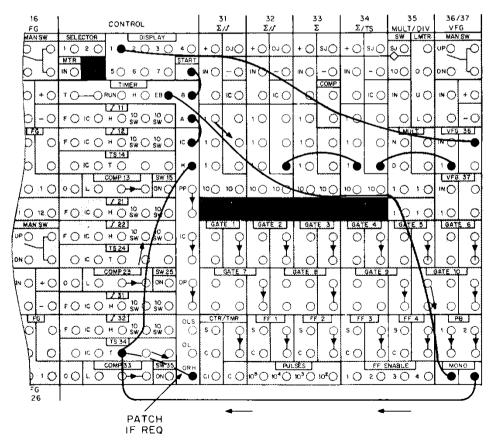

| 11.6             | Parameter Sweep: Patching                                                                               | 11-16 |

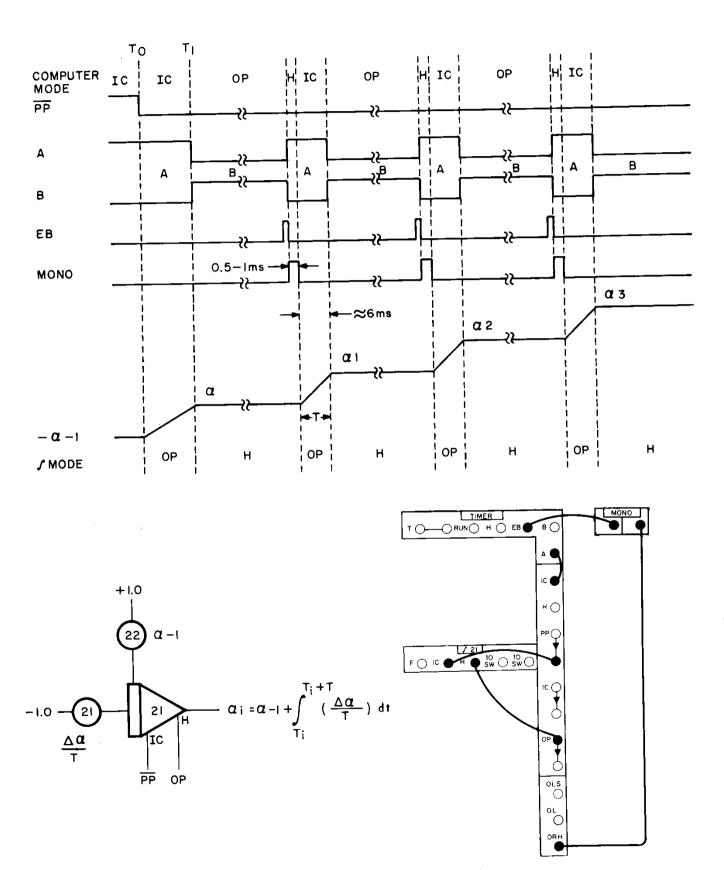

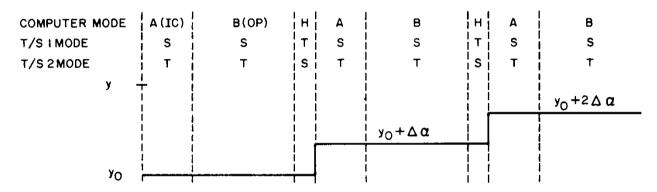

| 11.7             | Parameter Implementation with an Integrator                                                             | 11-18 |

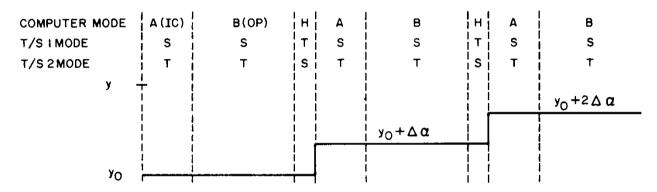

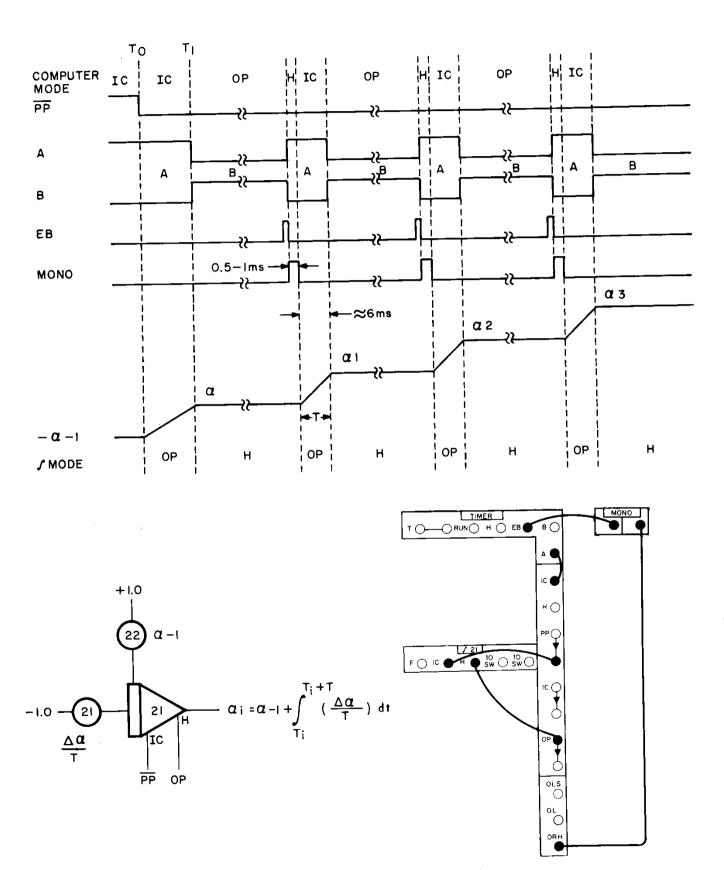

| 11.8             | Parameter Implementation with a Counter                                                                 | 11-19 |

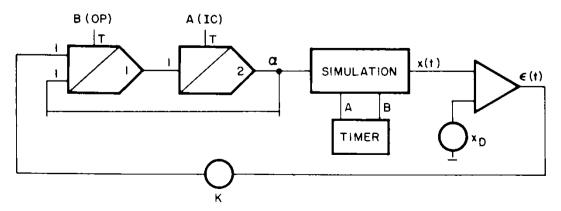

| 14.1             | Analog Mode and Time Scale: Controls and Patching Areas                                                 | 14-1  |

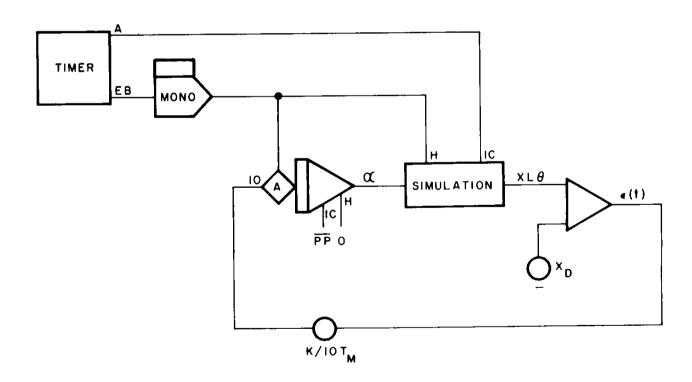

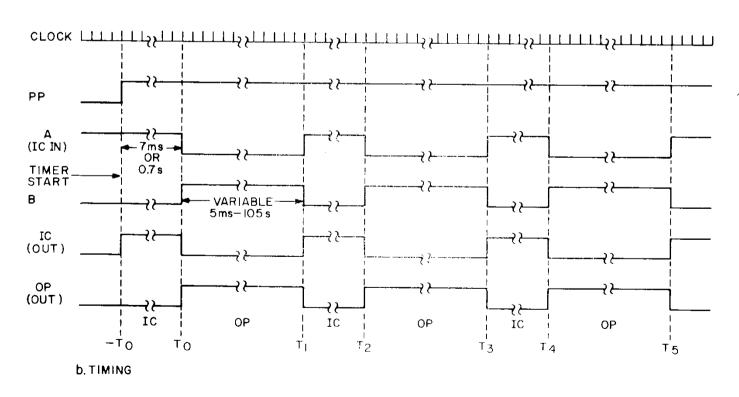

| 14.2             | Typical Repetitive Operation: Patching and Timing                                                       | 14-5  |

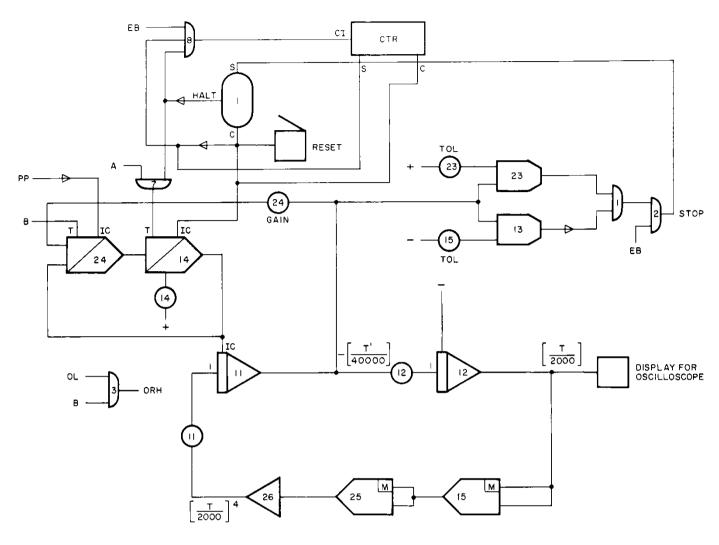

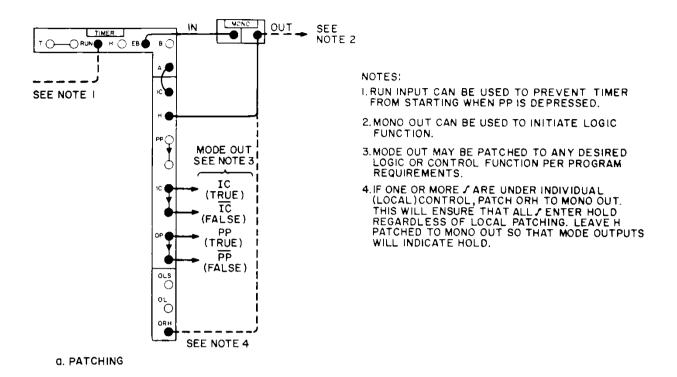

| 14.3             | Typical Three-Mode Iterative Operation: Patching and Timing                                             | 14-7  |

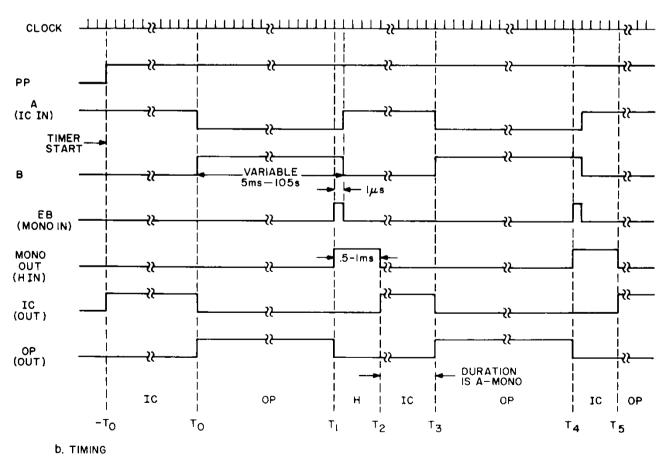

| 14.4             | Basic ORH and OLS Patching                                                                              | 14-8  |

| 14.5             | Integrator Mode and Time Scale: Local Control Patching                                                  | 14-10 |

| 14.6             | Track-Store: Local Control Patching                                                                     | 14-11 |

| 15.1             | Logic Clock and Logic Mode: Patching Areas and Controls                                                 | 15-1  |

| 16.1             | Readout Controls and Patching Areas                                                                     | 16-1  |

| 16.2             | Signal Selector System: Simplified Diagram                                                              | 16-3  |

| 17.1             | Overload and Status Indicator Locations                                                                 | 17-1  |

| 18.1             | Potentiometer: Circuit and Symbol                                                                       | 18-1  |

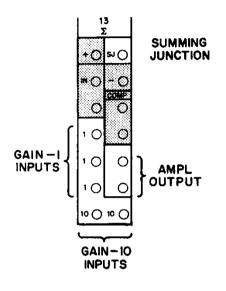

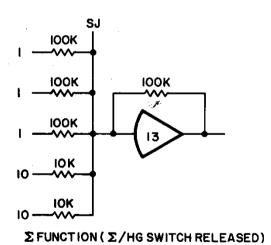

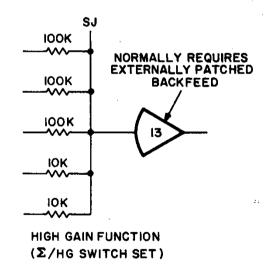

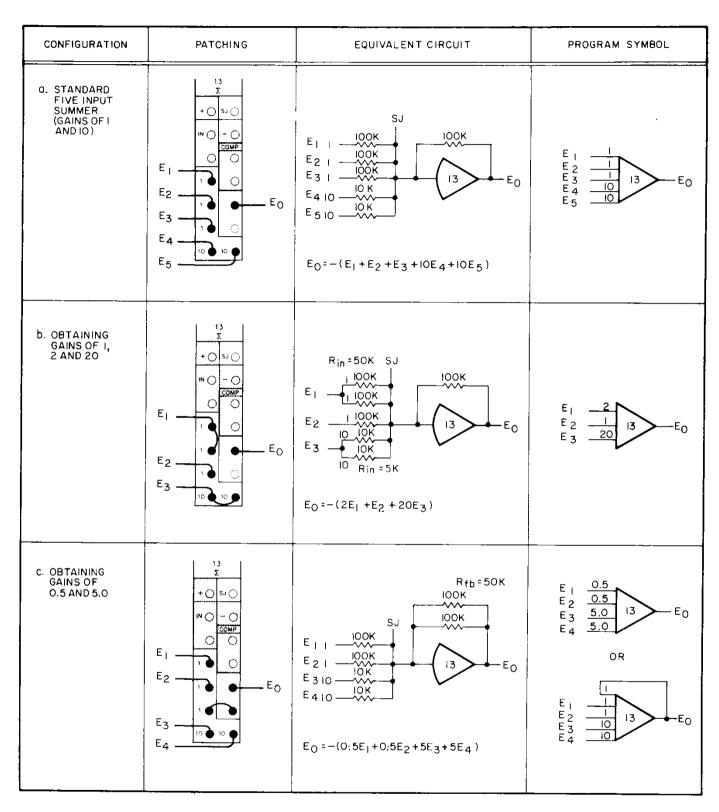

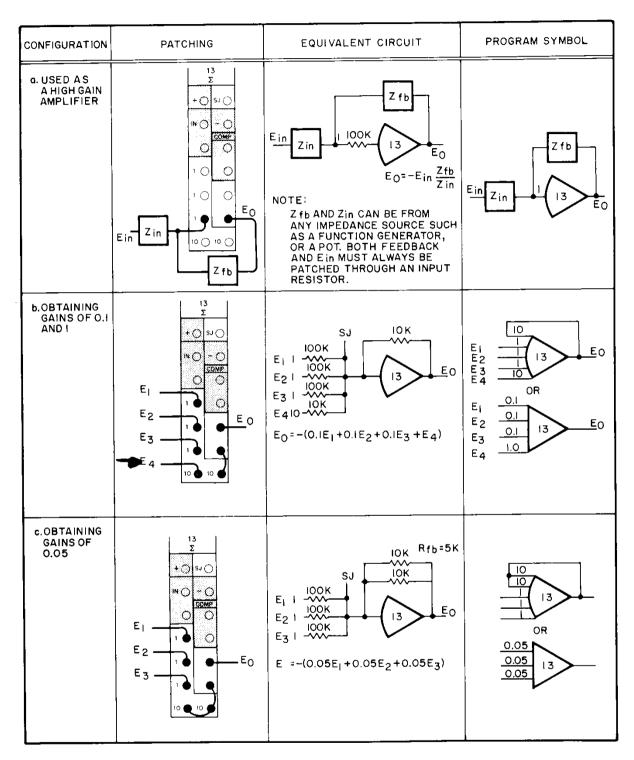

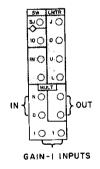

| 19.1             | Summer/High Gain: Simplified and Equivalent Circuits                                                    | 19-1  |

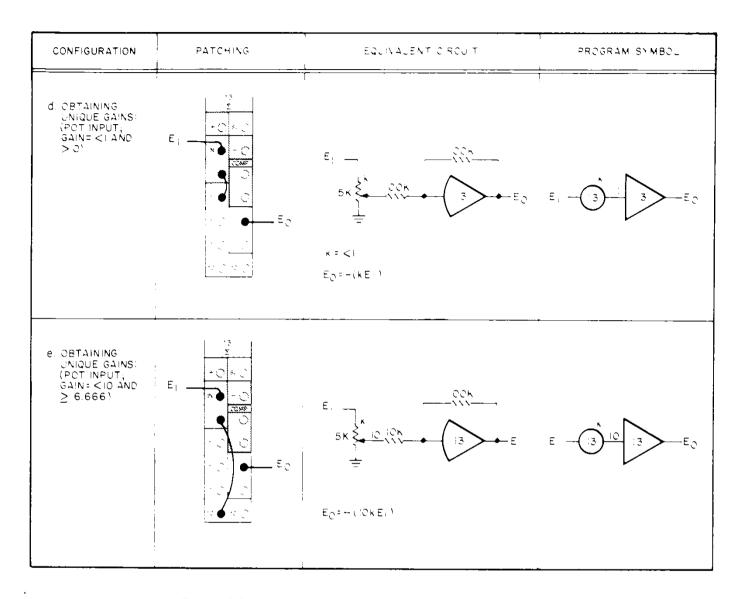

| 19.2             | Summer Patching: $\Sigma/HG$ Switch Released (Out)                                                      | 19-2  |

| 19.3             | High-Gain Patching: $\Sigma$ /HG Switch Set (In)                                                        | 19-4  |

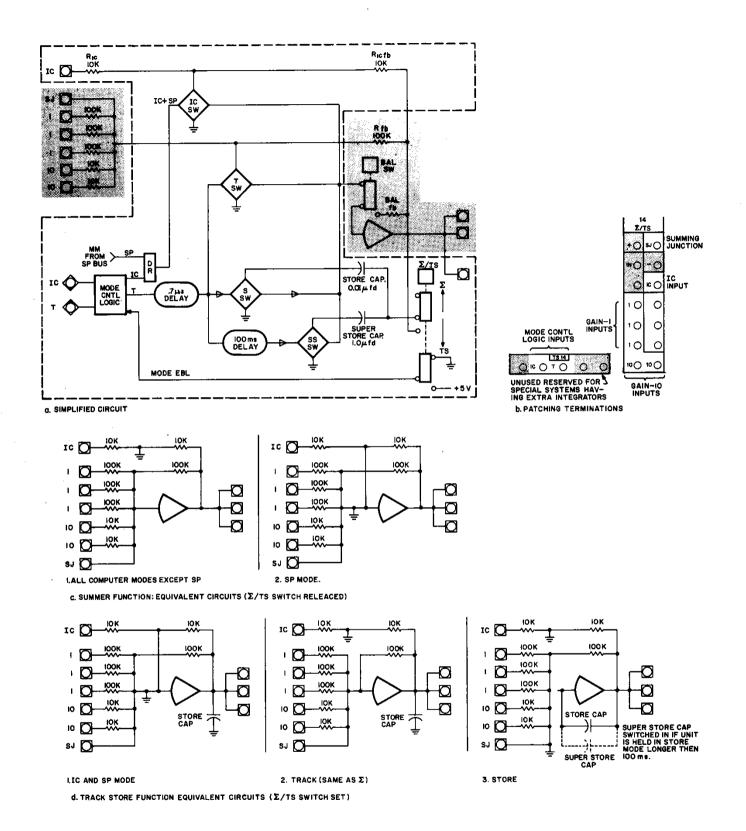

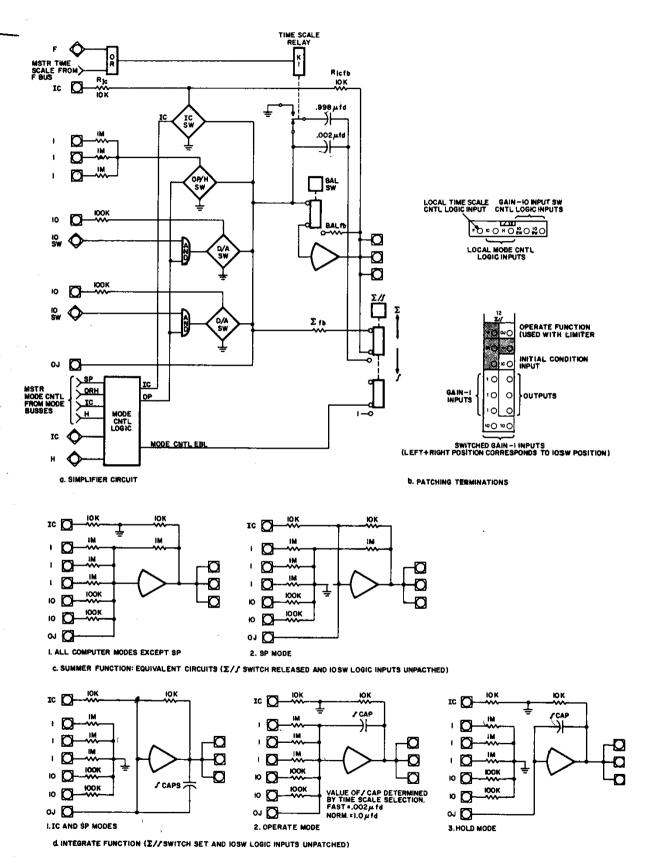

| 20.1             | Summer/Track-Store: Simplified and Equivalent Circuits                                                  | 20-1  |

| 20.2             | Typical Track-Store Operation                                                                           | 20-2  |

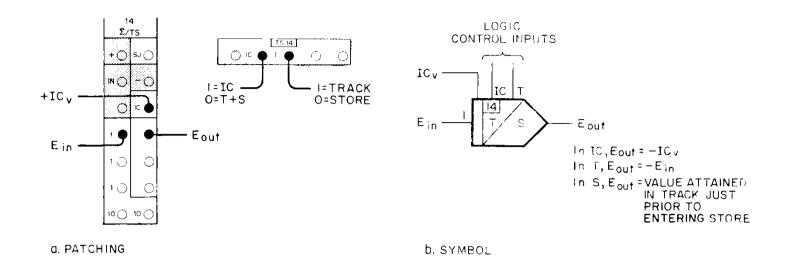

| 20.3             | Basic Track-Store Patching                                                                              | 20-3  |

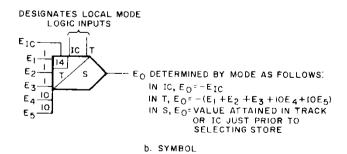

| 21.1             | Summer/Integrator: Simplified and Equivalent Circuits                                                   | 21-1  |

| 21.2             | Summer Patching: $\Sigma/\int$ Switch Released (Out)                                                    | 21-2  |

| 21.3             | Integrator Patching: $\Sigma/\int$ Switch Set (In)                                                      | 21-3  |

| 21.4             | Patching the $\Sigma/\mathcal{a}$ as a Track-Store Amplifier: $\mathcal{L}/\mathcal{a}$ Switch Set (In) | 21-4  |

| 21.5             | Gain — 10 Switching                                                                                     | 21-5  |

### **ILLUSTRATIONS (CONT)**

| Figure<br>Number | Title                                                               | Page          |

|------------------|---------------------------------------------------------------------|---------------|

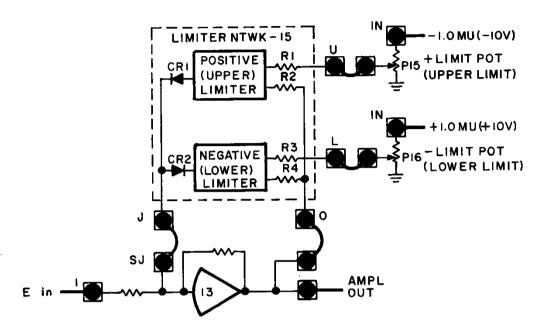

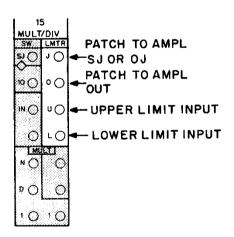

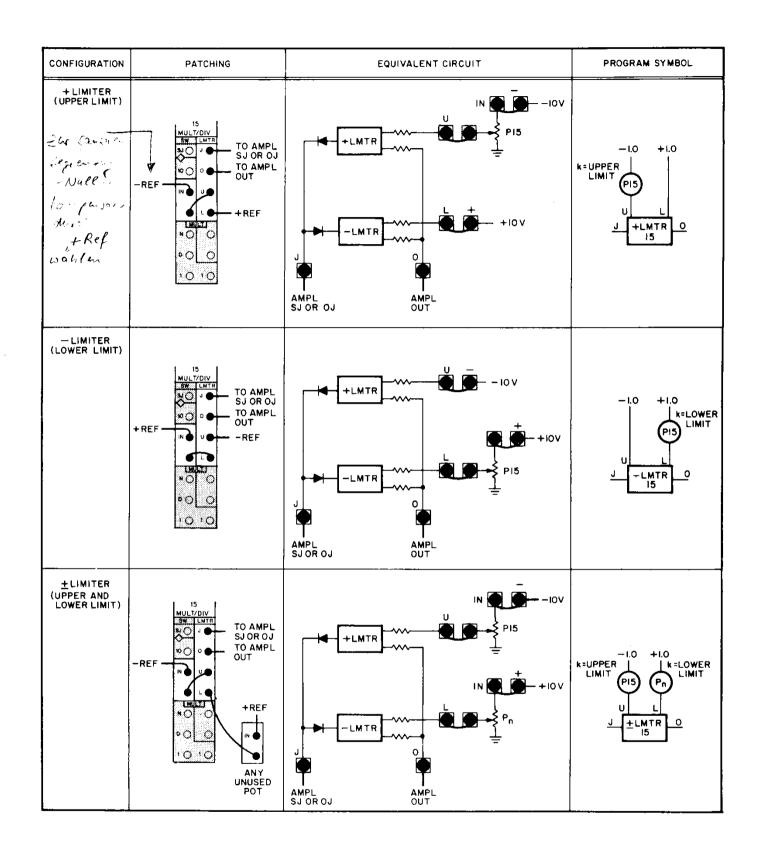

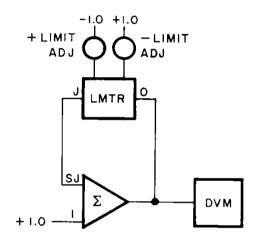

| 22.1             | Simplified Limiter Circuit: Used with Typical Amplifier             | . 22-1        |

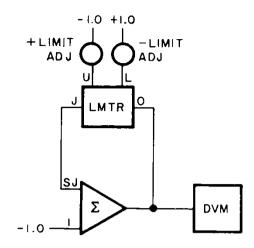

| 22.2             | Limiter: Patching and Equivalent Circuit                            | . 22-2        |

| 22.3             | Limiter Setup                                                       | . 22-3        |

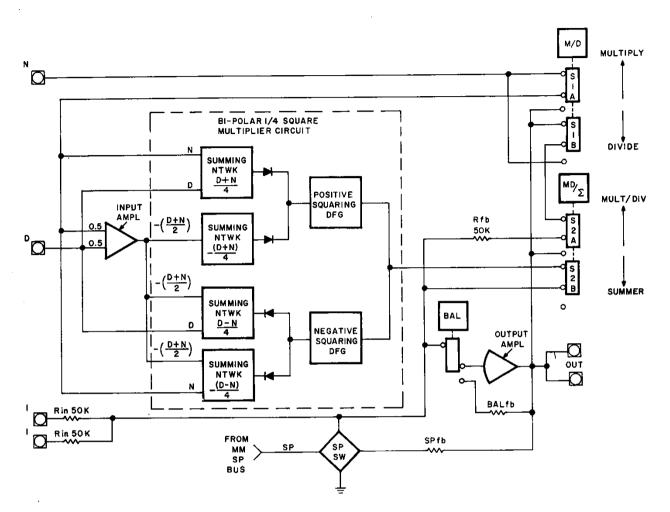

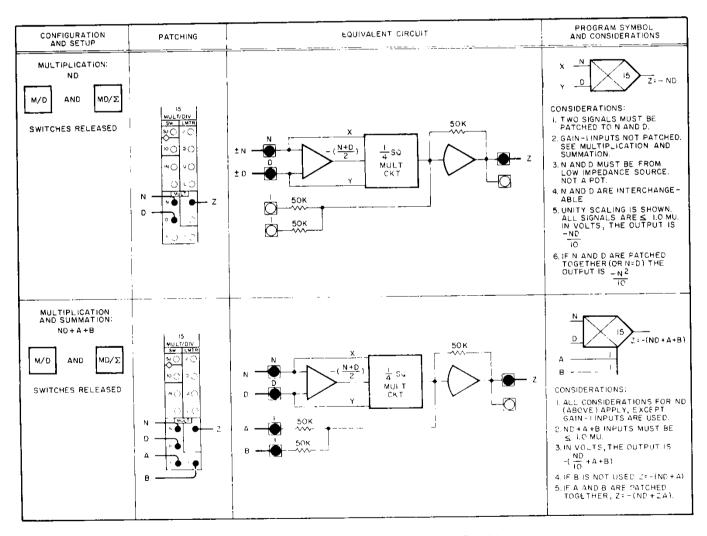

| 23,1             | Multiply/Divide Unit: Simplified Circuit                            | . 23-1        |

| 23.2             | Multiply/Divide Unit: Setup and Patching                            | . 23-2        |

| 24.1             | Log/Exponent Function Generator: Simplified and Equivalent Circuits | . 24-1        |

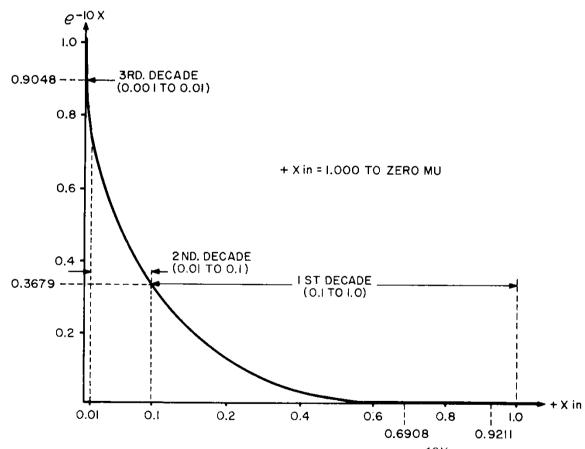

| 24.2             | The Logarithmic Curve (0.1 Inx)                                     | . 24-1        |

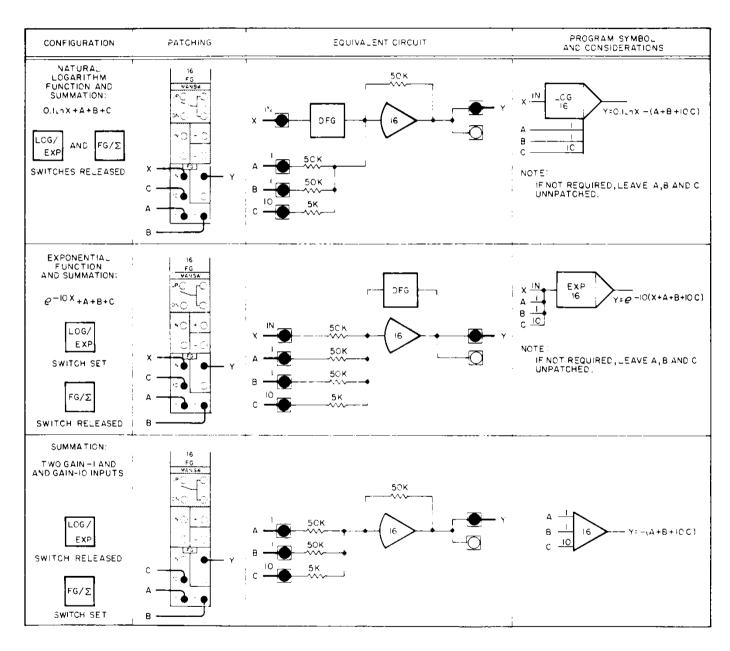

| 24.3             | The Exponential (Antilog) Curve (e <sup>-10×</sup> )                | . 24-2        |

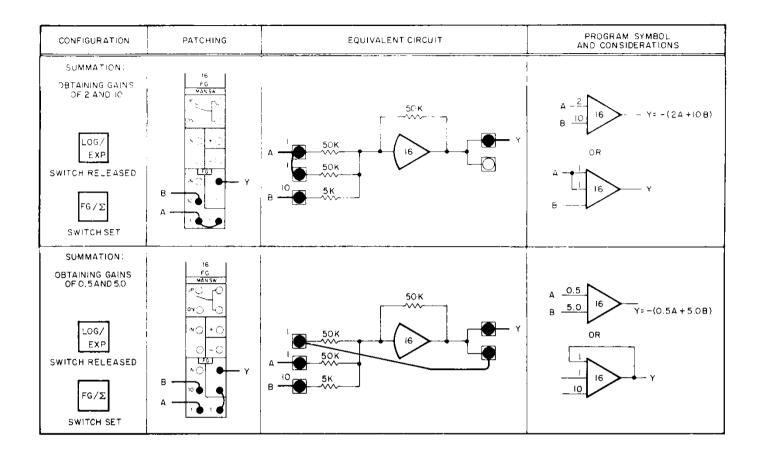

| 24.4             | Log/Exρ Function Generator: Setup and Patching                      | . 24-3        |

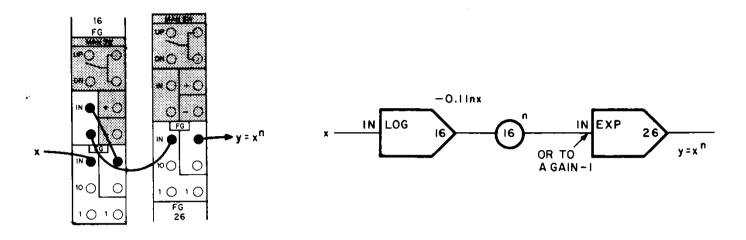

| 24.5             | Generating X <sup>n</sup>                                           | . 24-5        |

| 25.1             | VFG: Controls and Patching Area                                     | . <i>25-1</i> |

| 25.2             | Typical Diode Segment                                               | . 25-2        |

| 25.3             | VFG Modes and Equivalent Circuits                                   | . 25-3        |

| 25.4             | Sample Ten Segment Function                                         | . 25-5        |

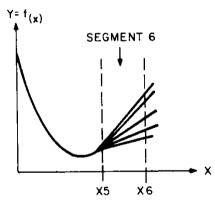

| 25.5             | Effect of Changing Slope Pot Y6 on VFG Output                       | . 25-6        |

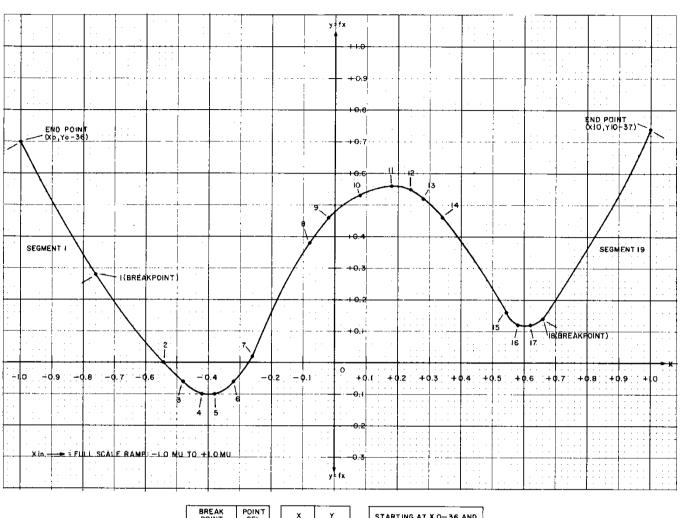

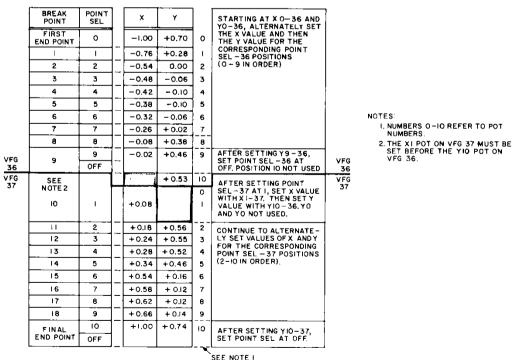

| 25.6             | Sample 19 Segment Function                                          | 25-11         |

| 25.7             | Typical Setup for Plotting A Function                               | 25-12         |

| 25.8             | VFG: Basic Patching                                                 | 25-14         |

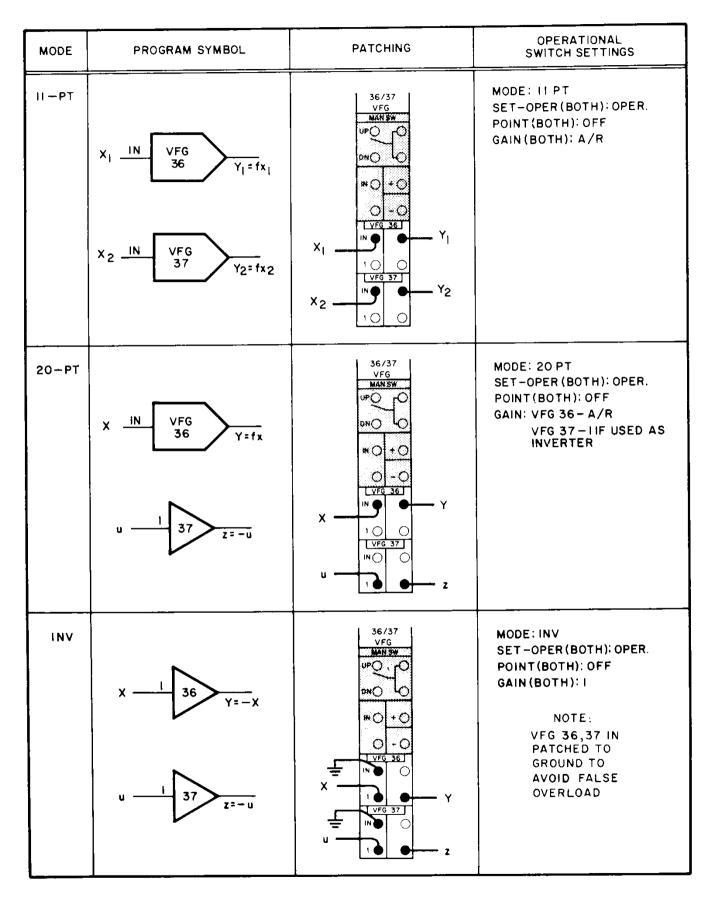

| 26.1             | Gates: Simplified Circuits                                          | . 26-1        |

| 26.2             | Gate Patching                                                       | . 26-1        |

| 26.3             | Typical AND Gate Fan-Out Circuit                                    | . 26-3        |

| 26.4             | Typical Method of Cascading Gates                                   | . 26-3        |

| 27.1             | The Pushbutton Flip-Flop                                            | . 27-1        |

| 27.2             | The General Purpose Flip-Flop                                       | . 27-2        |

| 27.3             | GPFF: Basic Patching and Operating Information                      | . 27-4        |

| 27.4             | GPFF: Patching and Timing                                           | . 27-5        |

| 27.5             | Using the GPFF to Form a Register                                   | . 27-7        |

| 28.1             | Manual Switch: Patching and Operating Information                   | . 28-1        |

| 28.2             | D/A Switch: Patching and Operating Information                      |               |

| 28.3             | The Comparator                                                      |               |

| 28.4             | Comparator Patching                                                 | . 28-4        |

|                  |                                                                     |               |

### **ILLUSTRATIONS (CONT)**

| Figure<br>Number | Title                                                                |        |  |  |  |  |  |

|------------------|----------------------------------------------------------------------|--------|--|--|--|--|--|

| 29.1             | The Interval Timer                                                   | . 29-1 |  |  |  |  |  |

| 29.2             | Typical Use (Run and H Unpatched): Timer Starts when PP is Depressed | . 29-4 |  |  |  |  |  |

| 29.3             | Typical Use of RUN: Delayed Start                                    | . 29-5 |  |  |  |  |  |

| 29.4             | Typical Use of H: Extended B (OP) Interval                           | . 29-6 |  |  |  |  |  |

| 29.5             | The Counter/Timer                                                    | . 29-8 |  |  |  |  |  |

| 29.6             | Event Counter: Patching and Timing                                   | 29-10  |  |  |  |  |  |

| 29.7             | One-Shot: Patching and Timing                                        | 29-11  |  |  |  |  |  |

| 29.8             | Frequency Divider: Patching and Timing                               | 29-13  |  |  |  |  |  |

| 29.9             | The MONO                                                             | 29-13  |  |  |  |  |  |

### **TABLES**

| Table<br>Number | Title                                                   | Page   |

|-----------------|---------------------------------------------------------|--------|

| 2.1             | Equipment Complement: Analog Components                 | 2-1    |

| 2.2             | Equipment Complement: Logic Components                  | 2-3    |

| 2.3             | Equipment Complement: Analog/Logic Interface Components | 2-3    |

| 2.4             | Patch Panel Field Assignments for Analog Components     | 2-7    |

| 2.5             | Analog Control Panel: Controls and Indicators           | 2-11   |

| 2.6             | Logic Control Panel: Controls and Indicators            | 2-14   |

| 2.7             | Setup Switch Functions                                  | 2-17   |

| 11.1            | Shift Register Operation                                | . 11-9 |

| 14.1            | The Time Scales                                         | . 14-2 |

| 14.2            | PP Master Mode Truth Table                              | . 14-3 |

| 14.3            | Master Mode Patch Panel Outputs                         | . 14-4 |

| 15.1            | Clock Downcounter: Output Frequencies and Periods       | . 15-3 |

| 16.1            | Device Addressing (SELECTOR-1)                          | . 16-1 |

| 25.1            | 11-Point Table of Values                                | . 25-7 |

| 25.2            | Sample Order of Procedure (Ten-Segment Function)        | . 25-8 |

| 29.1            | Timer Range Versus SECONDS Switch Setting               | . 29-2 |

| 29.2            | Timer Patch Panel Terminations                          | 29-2   |

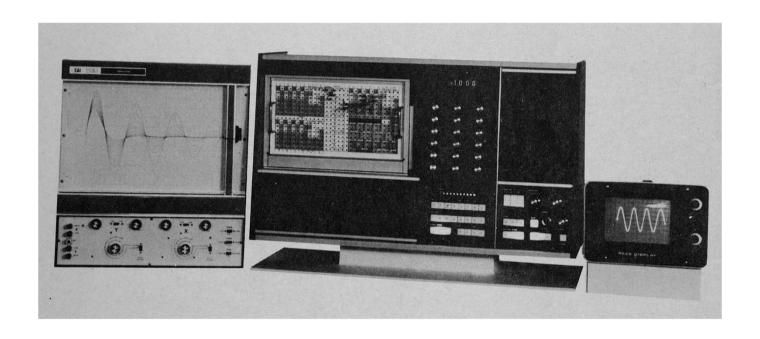

Figure 1.1 Typical MiniAC Computing System

#### INTRODUCTION

#### 1.1 THE EA! MiniACTM (Figure 1.1)

The EAI MiniAC is an educational analog/hybrid simulation system specifically designed for technical colleges, university engineering and science departments, and industrial training groups. Peripherals that can be used with the MiniAC include an X-Y Plotter, and a display scope.

The MiniAC Console is the major system component and is a self-contained 10 volt reference analog computer. This computer contains analog and logic computational components, control logic, hybrid (analog/logic interface) components, and operating controls. A basic system can solve a non-linear second-order differential equation with an imposed limit and has provisions for an analog comparison and logical operation. A fully expanded system can solve an automatic optimization and plot two to three non-linear third order differential equations. Problems are introduced at a removable patch panel; the removable feature permits storage of programmed problems.

#### 1.2 PURPOSE OF MANUAL

This manual is written with three specific goals in mind:

- 1. To familiarize *all users* with the computer organization and patching facilities, the basic functions of the various operating controls and indicators, and the general operation of the system as a whole.

- 2. To provide a guide for *the occasional user or trainee* that allows him to patch and run his particular problem without delving into circuit related details.

- 3. To provide the *relatively experienced user* those details that will permit him to utilize the MiniAC to its fullest extent.

#### 1.3 STRUCTURE OF MANUAL

To achieve the above goals, this manual is divided into three separate and distinct parts as follows:

PART 1 - FAMILIARIZATION AND GENERAL OPERATION

PART 2 - USERS GUIDE

PART 3 - REFERENCE HANDBOOK

Each part of this manual is divided into three or more chapters. All chapters are numbered consecutively within a part, and from part-to-part.

#### PART 1 - FAMILIARIZATION AND GENERAL OPERATION

Is oriented toward all users and consists of Chapters 1 through 3. Describes the overall system, locates and identifies all major components, and contains general operating information for the computer as a whole. The user should be completely familiar with PART 1 before attempting to use the MiniAC or before proceeding to either PART 2 or 3.

#### PART 2 - USERS GUIDE

Consists of Chapters 4 through 12. This portion of the manual is directed at the infrequent user and/or the trainee. Part 2 is oriented toward problem solving and carries the user from patching and setting up the simplest mathematical function all the way up to patching and running a sample two point boundary value problem.

#### PART 3 - REFERENCE HANDBOOK

The reference handbook portion of this manual (Chapters 13 through 29) is directed toward the frequent or relatively experienced user. Part 3 describes in detail the workings of the MiniAC subsystem by subsystem and component by component. Sufficient information is provided to permit the experienced programmer to fully utilize all programmable features to devise unique patching schemes on a subsystem and an individual component basis.

#### 1.4 HOW TO USE THIS MANUAL

First, read Part 1 to become thoroughly familiar with the organization of the machine, the patch panel, the basic function of the various controls and indicators, and the general operating procedures. Then, if reasonably on board with Analog Programming and analog computers in general, refer to the reference handbook portion of the manual. If this is your first introduction to an analog computer or you have seldom used one, it is advisable to proceed directly to the Users Guide. In either case (experienced or trainee), a cursory review of the Table of Contents will aid you in locating specific information required to patch and run your particular problem.

#### MACHINE ORGANIZATION

#### 2.1 INTRODUCTION

This chapter provides information to acquaint the user with the appearance, location, and basic functions of major components of the EAI MiniAC. Figure 1.1 illustrates a typical system with peripheral devices. The MiniAC is the heart of the system and contains all necessary analog programming facilities, computing elements, control features, and basic monitoring devices. All uncommitted programmable components are terminated at the patch panel and are interconnected with patch cords as required by the specific program. The peripheral devices permit the operator to interact with the master program and graphically record or document instantaneous problem solutions. The following paragraphs give a brief description of those portions of the console (Figure 2.1) that are of prime importance to the programmer/operator.

#### 2.2 THE ANALOG COMPONENTS

A fully expanded MiniAC provides an array of analog computational devices. Table 2.1 lists the analog equipment complement provided with a fully expanded MiniAC. This table also includes specific chapter references in which each component is described. With the exception of the manual switches, coefficient potentiometers, and the variable function generator, all analog components that perform mathematical functions are located directly behind the setup switch/overload indicator panel.

Table 2.1. Equipment Complement: Analog Components

| _                                                                                                               |             | Cha           | apter Reference    |

|-----------------------------------------------------------------------------------------------------------------|-------------|---------------|--------------------|

| Component                                                                                                       | Quantity    | Users Guide   | Reference Handbook |

| Linear (Including those associated with multipliers, function generators, etc.): Summer/Integrator $(\Sigma/f)$ | 6           | 5             | 21                 |

| Five-Input Summer/High Gain ( $\Sigma$ )                                                                        | 3           |               | 19                 |

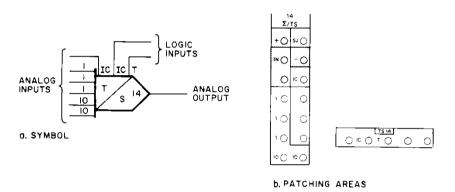

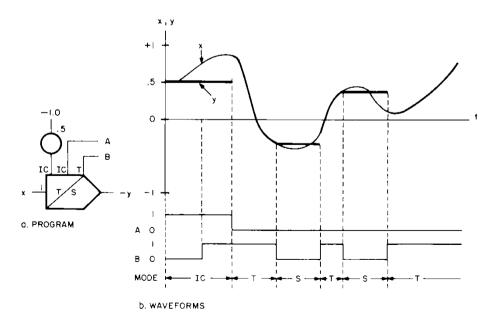

| Five-Input Summer/Track Store ( $\Sigma$ /TS)                                                                   | 3           |               | 20                 |

| Two-Input Summer/Inverter (MULT/DIV)                                                                            | 3           |               | 23                 |

| Three-Input Summer (FG)                                                                                         | 2           |               | 24                 |

| Inverter (VFG)                                                                                                  | 2           | <b>∀</b><br>5 | 25                 |

| Potentiometers                                                                                                  | 18          | 5,6           | 18                 |

| Non-Linear:                                                                                                     | · · · · · · |               | -                  |

| Multiplier (MULT/DIV):                                                                                          | 3           | 5             | 23                 |

| Function Generators:                                                                                            |             |               |                    |

| Log/Exponential                                                                                                 | 2           | 5             | 24                 |

| Variable (10 Segment)                                                                                           | 2           | 7             | 25                 |

| Interval Timer:                                                                                                 | 1           | 9,10          | 29                 |

| Manual Switches:                                                                                                | 3           | 5             | 28                 |

| Trunks:                                                                                                         | 12          | -             | 14                 |

| Digital Voltmeter (DVM)                                                                                         | 1           | 6             | 16                 |

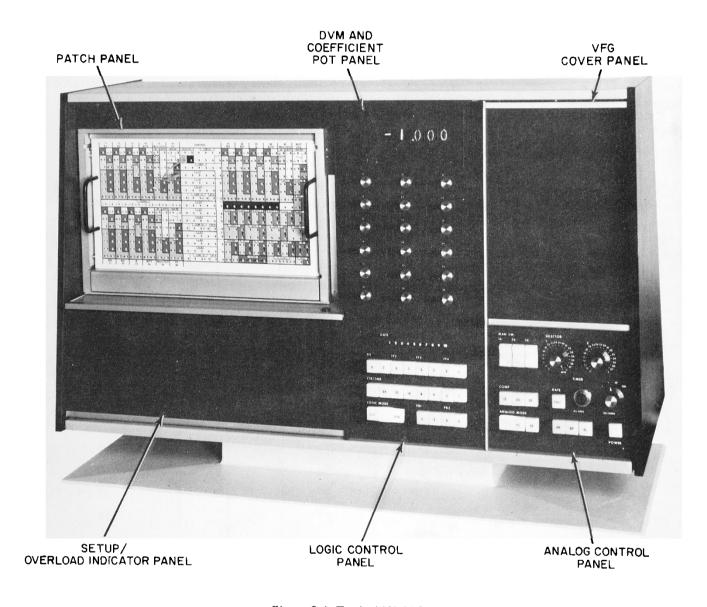

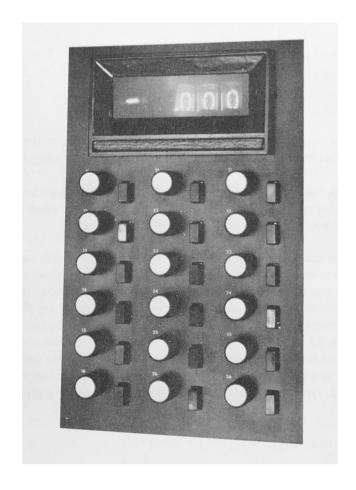

Figure 2.1. Typical MiniAC

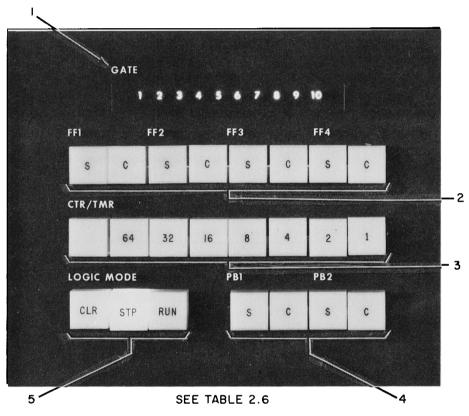

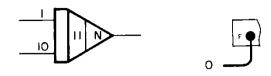

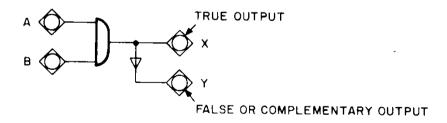

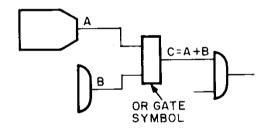

#### 2.3 THE LOGIC COMPONENTS

The various logic elements available for use in the MiniAC provide operational flexibility to physical system simulation. These logic elements permit simulation of descrete and continuous systems and provide a wide range of flexibility in problem control. In other words, a logical event can be used to control an analog function and vice versa. All logic elements (such as pushbutton flip-flops, general purpose flip-flops, and the counter/timer) are physically located directly behind the logic control panel (Figure 2.1). Table 2.2 lists the equipment complement provided with the logic expansion and specifies the chapter(s) in which each component is described.

Table 2.2. Equipment Complement: Logic Components

| Component                            | Quantity | Chapter Reference |                    |  |

|--------------------------------------|----------|-------------------|--------------------|--|

|                                      | Quantity | Users Guide       | Reference Handbook |  |

| Gates:                               |          |                   |                    |  |

| Two Input                            | 6        | 11                | 20                 |  |

| Four Input                           | 4        | ''                | 26                 |  |

| Counter/Timer:                       | 1        | 11                | 29                 |  |

| Flip-Flops:                          |          |                   |                    |  |

| General Purpose                      | 4        | 11                | 0.7                |  |

| Pushbutton                           | 2        | ''                | 27                 |  |

| Monostable Multivibrator (One Shot): | 1        | 11                | 29                 |  |

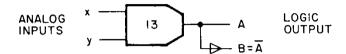

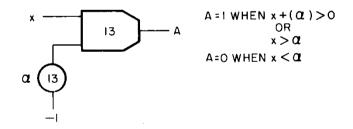

### 2.4 THE ANALOG/LOGIC INTERFACE COMPONENTS

Analog/logic interface components provide interface and control between the analog and logic portions of a program. These devices include analog controlled digital (A/D) comparators and digital controlled analog (D/A) switches.

The equipment complement of analog/logic interface components is listed in Table 2.3. This table also includes specific chapter references in which these devices are described. Like the analog and logic components, these hybrid devices are terminated at the patch panel.

Table 2.3. Equipment Complement: Analog/Logic Interface Components

| Component                          | Quantity | Chapter Reference |                    |  |

|------------------------------------|----------|-------------------|--------------------|--|

|                                    | Quantity | Users Guide       | Reference Handbook |  |

| A/D Comparators:                   | 3        | 5                 | 28                 |  |

| D/A Switches:                      |          |                   |                    |  |

| Uncommitted (SW)                   | 3        | 5                 | 28                 |  |

| Summer/Integrator Committed (10SW) | 12       | 5                 | 21                 |  |

#### 2.5 THE CONTROL AND MONITORING SYSTEMS

The MiniAC is equipped with versatile control and monitoring systems that permit: selection of addressable analog components for value readout and display; control of analog time scale; control of analog and logic modes; and slave operations. Complete monitoring facilities are provided that permit status readout of logic elements as well as indicating amplifier overload conditions. All aspects of these systems are described in Chapters 14 through 17 of the Reference Handbook.

#### 2.6 THE PATCH PANEL

#### 2.6.1 INTRODUCTION

The following paragraphs describe the patch panel layout. This includes: general patch panel location of individual components and controls; the component location numbering system (address); and general color coding information. Detailed information concerning patch panel layout for individual components and controls (including patching techniques and methods) are given in subsequent chapters describing the specific component or control system.

The removable panel (Figure 2.2) provides readily accessable termination and interconnection points for assembling (patching) devices that perform mathematical and logical functions in any array required to obtain a given problem solution. The patch panel also provides patching facilities for problem control purposes and problem solution outputs.

Patching is the act of interconnecting the mathematical and logical elements so that the assembled (patched) devices correspond to the "paper" program. Patching may be performed with the panel on the computer, or "off-line". If more than one patch panel is available, a problem may be prepatched (remotely from the machine) while another problem is being run. In other words, one user can produce a problem solution while another is preparing a problem. The availability of multiple patch panels permits retaining (storing) a patched problem or simulation that may be used frequently for demonstration or other purposes.

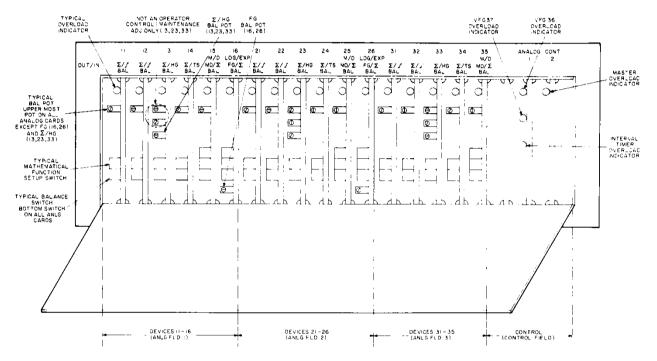

#### 2.6.2 PATCH PANEL LAYOUT

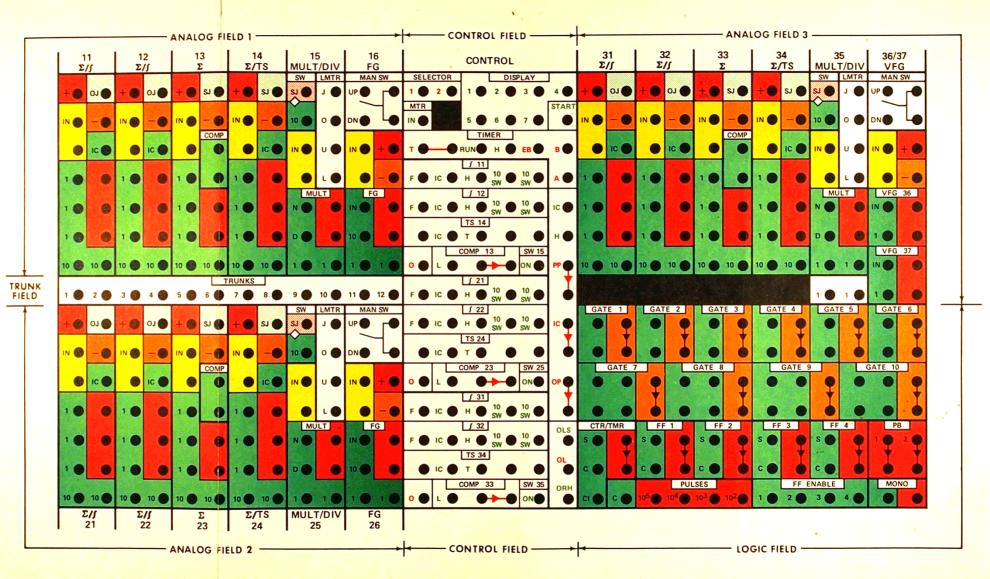

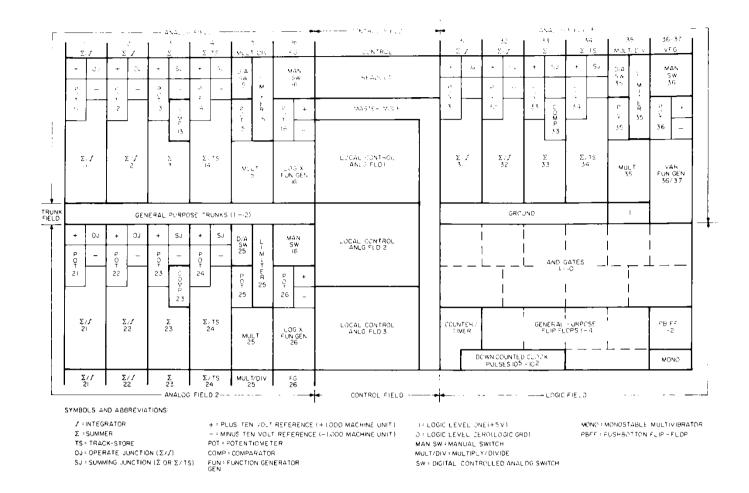

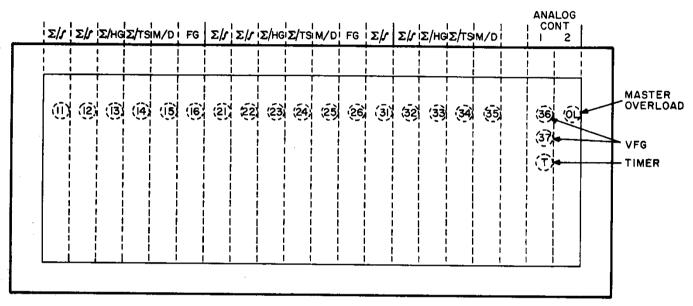

#### 2.6.2.1 General

For ease in programming and locating components for patching, the MiniAC patch panel is divided into symmetrical fields. Basically, there are three nearly identical analog fields, an analog trunk field, a logic field, and a control field. Each field is distinct and readily identified. Figure 2.3 is a simplified diagram of the patch panel and shows the general patching outlines and areas associated with each field. As an aid in identifying the various patching areas, compare this illustration to the patch panel details shown in Figure 2.2.

Figure 2.3. General Patching Areas

#### 2.6.2.2 The Analog Fields

Basically, each analog field is divided into six rectangular patching areas, or modules. Each module provides terminations for at least two analog components. For patching convenience, each module includes terminations for a potentiometer, and computer reference (±1.0 machine units) is distributed throughout each field.

A two digit number embossed on the patch panel identifies the patching module and the field. The first digit (1-3) is the field designation. The second digit is the assigned module number (1-6). For example, the fifth patching module in field one is assigned the number 15 (field 1, module 5). Therefore, analog components terminated in this field/module are identified by the number 15.

In addition to the field/module numbering system, modules are further identified by a symbol or mnemonic designation that indicates the major computing component terminated in that module. For example, modules 1 and 2 in each field are marked with the  $\Sigma/f$  symbol (Figures 2.2 and 2.3). This indicates that the major computing

component terminated in these modules is the summer/integrator. Table 2.4 lists each component and facility terminated in the patch panel analog field, identifies each by symbol or mnemonic designation and module number, and lists the quantity per field.

Table 2.4. Patch Panel Field Assignments for Analog Components

|                                  | Symbol                       |                  | Quantit |        |   |        |

|----------------------------------|------------------------------|------------------|---------|--------|---|--------|

| Analog Component or Facility     | or Mnemonic<br>Panel Marking | Module<br>Number | 1       | 2      | 3 | Totals |

| Summer/Integrator                | Σ/∫                          | 1,2              | 2       | 2      | 2 | 6      |

| Summer/High Gain                 | Σ                            | 3                | 1       | 1      | 1 | 3      |

| Comparator                       | СОМР                         | 3                | 1       | 1      | 1 | 3      |

| Summer/Track Store               | Σ/TS                         | 4                | 1       | 1      | 1 | 3      |

| Multiplier                       | MULT/DIV                     | 5                | 1       | 1      | 1 | 3      |

| Digital Controlled Analog Switch | SW                           | 5                | 1       | 1      | 1 | 3      |

| Limiter                          | LMTR                         | 5                | 1       | 1      | 1 | 3      |

| Log X Function Generator         | FG                           | 6                | 1       | 1      | 0 | 2      |

| Manual Switch                    | MAN SW                       | 6                | 1       | 1      | 1 | 3      |

| Variable Function Generator      | VFG                          | 6/7              | 0       | 0      | 2 | 2      |

| Potentiometer                    | None<br>(Colored             | 1-6              | 6       | 6      | 6 | 18     |

|                                  | coded                        |                  |         |        |   |        |

|                                  | yellow)                      |                  |         |        |   |        |

| Positive Reference               | +                            | 1-4,6            | 5       | 5      | 5 | 15     |

| Negative Reference               | _                            | 1-4,6            | 5       | 5      | 5 | 15     |

| Analog Ground                    | None                         | N/A              | 0       | 0      | 8 | 8      |

| S                                | (Color                       |                  |         |        |   |        |

|                                  | coded                        |                  |         | ł<br>I |   |        |

|                                  | black)                       |                  |         |        |   |        |

To simplify the process of patching a problem, the analog fields use a readily identifiable color code. The principle colors used are green, red, orange, yellow, white and black.

Green = Analog component inputs.

Red = Analog component outputs and positive reference.

Orange = Minus reference

Yellow = Potentiometers

White = Passive element manual switches and limiters

#### 2.6.2.3 The Trunk Field

The trunk field is located between analog fields one and two and is identified by the designation TRUNKS. These terminations provide 12 general purpose trunk lines for exchanging analog data with another computer or for use with external analog devices.

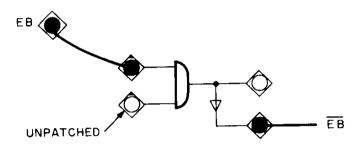

#### 2,6.2.4 The Logic Field

All logic computing elements are terminated in the patching area directly below Analog Field 3 (Figures 2.2 and 2.3). Logic component terminations are contained in a separate field to minimize cross-talk (noise pick-up) and to reduce the possibility of inadvertently patching an analog signal to a logic component, or vice versa.

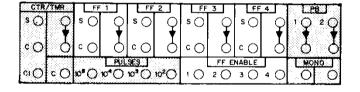

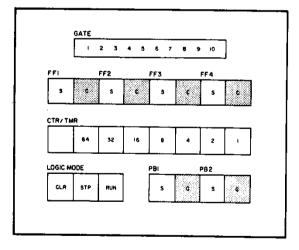

The logic field has provisions for program patching of: AND gates, a counter/timer; general purpose and pushbutton flip-flops, a monostable multivibrator, and down counted clock pulses. With the exception of AND gates, all logic outputs on the patch panel are synchronized with the system clock. Each logic component is identified by panel markings as indicated in the following list:

| Logic Component                     | Panel Designation                                                               | Quantity |

|-------------------------------------|---------------------------------------------------------------------------------|----------|

| Gates:                              | ,                                                                               |          |

| Two-Input                           | GATE 1 to GATE 6                                                                | 6        |

| Four-Input                          | GATE 7 to GATE 10                                                               | 4        |

| Counter/Timer                       | CTR/TMR                                                                         | 1        |

| General Purpose Flip-Flops          | FF1 to FF4                                                                      | 4        |

| Pushbutton Flip-Flops               | PB1 and PB2                                                                     | 2        |

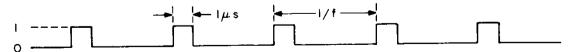

| Down Counted Clock                  | PULSES (10 <sup>5</sup> , 10 <sup>4</sup> , 10 <sup>3</sup> , 10 <sup>2</sup> ) | 4        |

| Monostable Multivibrator (One Shot) | MONO                                                                            | 1        |

To simplify the process of patching a problem, the logic field has a color code similar to that of the analog fields. The colors used are green, orange, and red. These indicate the following:

Green = Logic inputs (1 = +5V; 0 = GRD)

Orange = Asynchronous (unclocked) logic outputs.

Red = Synchronous (clocked) logic outputs.

Red on White = Logic level output.

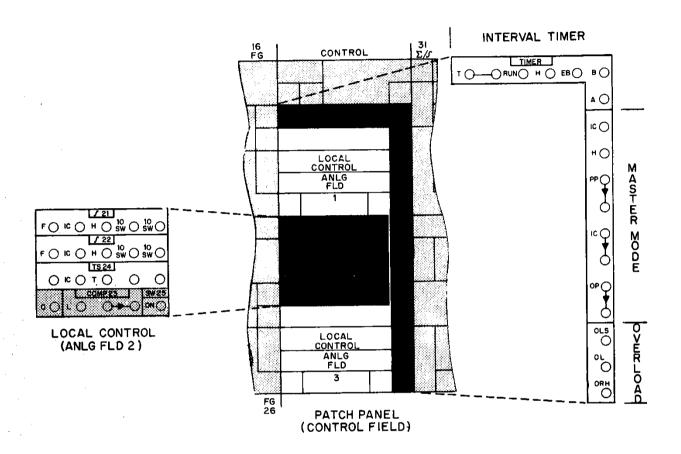

#### 2.6.2.5 The Control Field

The control field (Figures 2.2 and 2.3) is the white patching area separating analog fields 1 and 2 from analog field 3 and the logic field. Primarily, the control field provides patching facilities to permit logic signals to be used for individual component and computer mode control. The control field is functionally divided into three major areas as follows:

- 1. Readout Selection and Control

- 2. Master mode Control

- 3. Local Control

The readout area is located in the uppermost portion of the control field and permits patching the readout selector to external devices, as well as logic start/stop control of a remote display device (recorder or oscilloscope).

The inverted L shaped area below the readout termination group is devoted to logic control of computer modes. That is, if the patch panel (PP) is selected as master, the IC, H and OP modes can be selected by patching of logic signals. An interval timer is terminated in this area to permit automatic repetitive operations.

The patch panel provides terminations that permit individual logic control of analog components terminated in analog fields 1 through 3. Controlling individual analog components with logic levels patched at the control field is referred to as local control. Local control functions that can be performed by patching include: integrator time scale and mode; track-store/summer mode; D/A switch operation; and latch control of comparators. These logic control terminations are divided into three identical groups (one for each analog field) and are identified using the field/module numbering system described in Paragraph 2.6.2.2. To avoid confusion and for simplicity of patching, all local controls are marked with the corresponding field/module number and are further identified by the applicable symbol or mnemonic designation. As in the logic and analog fields, the control field is also color coded. However, in this case the panel symbol or lettering is color coded, not the background. The color codes used are green, red, and black. These indicate the following:

Green = Logic input in all areas, DISPLAY 1-7 and MTR-IN may also be used as analog inputs.

Red = Synchronous logic output or fixed logic level (0 = logic zero output).

Black = Analog ground.

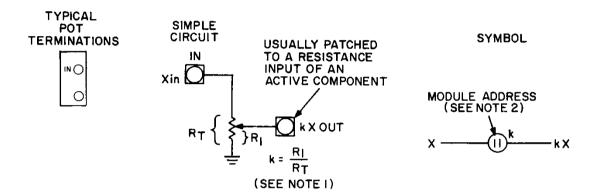

#### 2.7 DVM AND COEFFICIENT POT PANEL

The DVM and coefficient pot panel (Figure 2.4) contains the digital voltmeter (DVM) and the controls required to set constant coefficients into an analog program. The DVM displays the numeric value (in machine units) of any component selected for readout. Refer to Chapter 6 in the User's Guide or Chapter 16 in the Reference Handbook portion of this manual.

Problem coefficients are normally provided by the preset potentiometers mounted on this panel. These pots are arranged in three vertical columns with six in a column. Each pot is terminated at the patch panel and is identified by the numerical panel marking that corresponds to the patch panel address described in Paragraph 2.6. The individual pot knobs are used to preset the desired coefficient value. The pushbutton switches immediately to the right of each pot are used to display the pot output on the DVM. Pot setting procedures are given in Chapters 6 and 18 of the User's Guide and Reference Handbook respectively.

Figure 2.4. DVM and Coefficient Pot Panel

#### 2.8 THE VFG PANEL

The variable diode function generator (VFG) is located directly behind the removable VFG panel (Figure 2.1). This panel is only removed during set-up of the VFG and should remain in place at all other times to avoid inadvertently disturbing the VFG setup. The VFG is described in Chapter 7 of the User's Guide and Chapter 25 of the Reference Handbook.

#### 2.9 THE ANALOG CONTROL PANEL

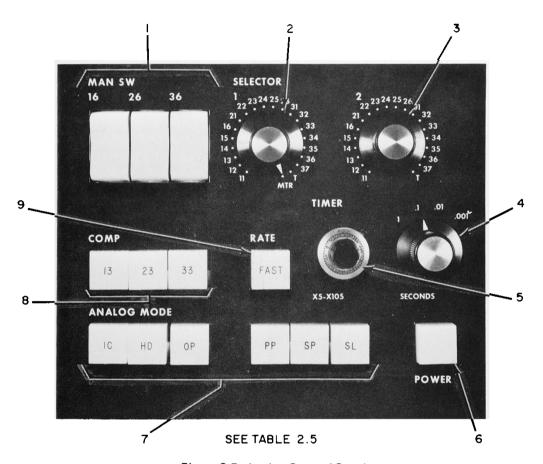

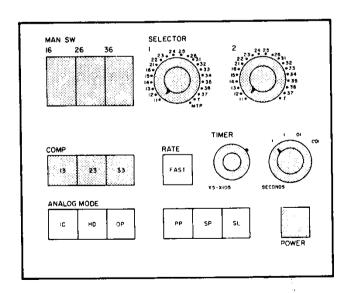

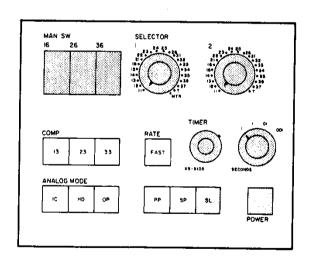

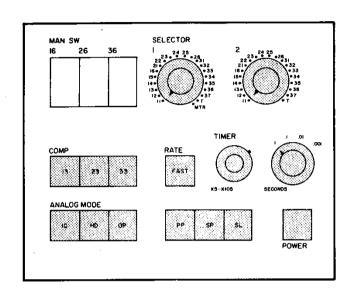

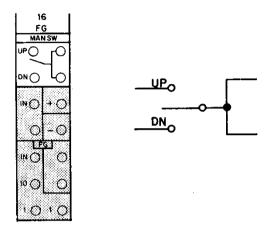

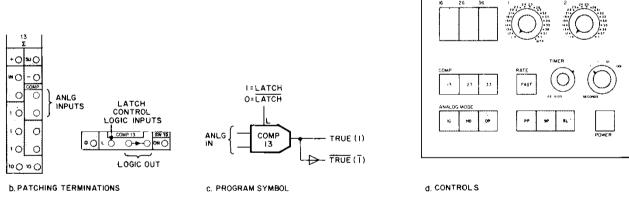

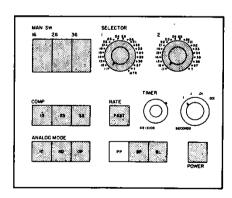

The analog control panel (Figure 2.5) is located at the right side of the MiniAC directly below the VFG panel. This control panel contains the power on switch; the computer analog mode controls; the time scale (rate) control; the interval timer controls; the readout signal selector; manual switches and manual controls for the comparators. The basic description and function of each control and indicator is given in Table 2.5.

Figure 2.5. Analog Control Panel

Table 2.5. Analog Control Panel: Controls and Indicators (Ref. Figure 2.5)

|              | Control or Indicator                               | or     |                                                                                                                                               |                                                                                                                 | ter Ref.       |             |

|--------------|----------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|-------------|

| Index<br>No. | Туре                                               | Desig. | Position<br>or Section                                                                                                                        | Function                                                                                                        | Users<br>Guide | Ref<br>Hdbk |

| 1            | 1 3-Position MAN SW<br>Toggle (16,26,36)<br>Switch |        | Used for manual control of analog functions.  Numbered designations correspond to patch panel address in which these switches are terminated. | 5                                                                                                               | 28             |             |

|              |                                                    |        | Up                                                                                                                                            | When up (top of switch flush with panel), UP termination on patch panel is connected to the switch wiper (arm). |                |             |

|              |                                                    |        | Down                                                                                                                                          | When down (bottom of switch flush with panel), DN termination is connected to switch wiper.                     |                |             |

|              |                                                    |        | Centered                                                                                                                                      | When centered, neither UP or DN is connected to switch wiper.                                                   |                |             |

(Cont)

Table 2.5. Analog Control Panel: Controls and Indicators (Continued)

|              | Contro                                      | ol or Indicato    | r                      |                                                                                                                                                                                                                                                                                                    | Chap | ter Ref.    |

|--------------|---------------------------------------------|-------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|

| Index<br>No. | Туре                                        | Desig.            | Position or Section    | Function                                                                                                                                                                                                                                                                                           |      | Ref<br>Hdbk |

| 2            | 21-Position<br>Rotary<br>Switch             | SELEC-<br>TOR-1   |                        | Selects addressed component for readout on DVM. Connects output of selected device to SELECTOR-1 output termination on patch panel.                                                                                                                                                                | 8    | 16          |

|              |                                             | ·                 | 11-37                  | Setting SELECTOR-1 at any one of these positions selects the amplifier output of the addressed device for readout as follows: $11,12,21,22,31,32=\Sigma/\int$ $13,23,33=\Sigma/HG$ $14,24,34=\Sigma/TS$ $15,25,35=MULT/DIV$ $16,26=FG$ $36,37=VFG$                                                 |      |             |

|              |                                             |                   | Т                      | Selects ramp output of timer for readout.                                                                                                                                                                                                                                                          |      |             |

|              |                                             |                   | MTR                    | Selects any signal patched to MTR-IN termination for readout.                                                                                                                                                                                                                                      |      |             |

| 3            | 20-Position<br>Rotary<br>Switch             | SELEC-<br>TOR-2   | 11-37<br>and T         | Connects output of addressed component to SELECTOR-2 patch panel terminations. All positions identical to SELECTOR-1 except there is no MTR position.                                                                                                                                              | 8    | 16          |

| 4            | 4-Position<br>Rotary<br>Switch              | TIMER-<br>SECONDS | 1<br>.1<br>.01<br>.001 | Selects duration and range of timer intervals as follows:         A Interval       B Interval         Pos.       (Approx.)       (Range)         1       0.7S       5S-105S         .1       0.7S       .5S-10.5S         .01       7 MS       50MS-1.05S         .001       7 MS       5MS-0.105S | 9,10 | 29          |

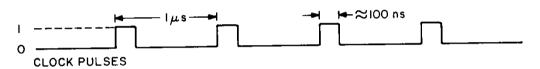

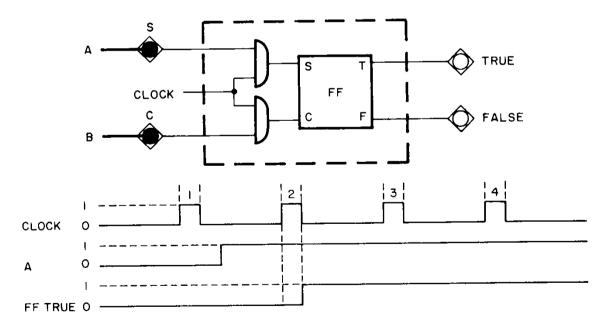

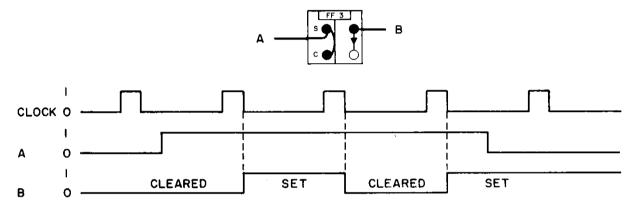

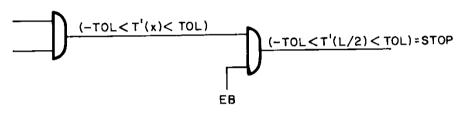

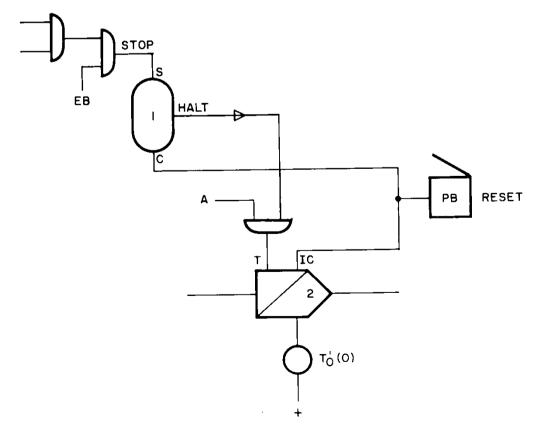

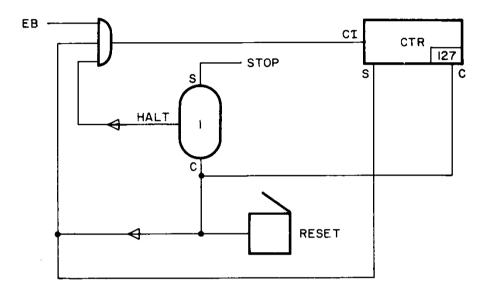

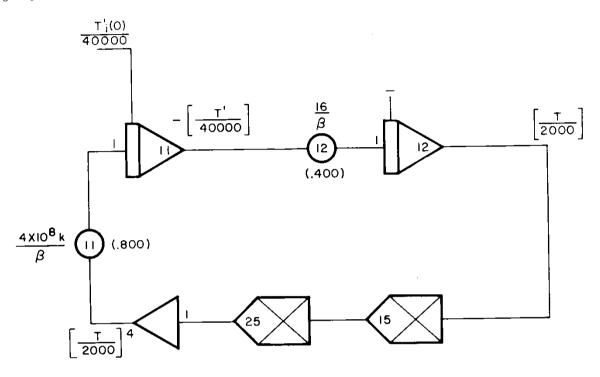

| 5            | 10 Turn<br>Calibrated<br>Potentiom-<br>eter | TIMER<br>X5-X105  | Adjustable             | Selects duration of Timer B interval. Direct dial readout is multiplied by TIMER-SECONDS switch setting.                                                                                                                                                                                           | 9,10 | 29          |